在IC卡公用电话系统中,在线式公用电话由于其具有保密性高、可扩展性强等特点,已逐渐获得人们的青睐。这种公用电话系统被置于终端和交换机之间,对两者的信号进行调制、解调以及其它的运算,来完成诸如卡验证、终端维护、多媒体信号传输等工作。与软件无线电相类似,这种系统的硬件平台通用性很强,数字信号处理的算法将由专门的芯片来承担,所以这种系统可以兼容目前在电话线上应用的各种调制解调方法,也可以适应未来出现的其它调制解调标准。

由此可以看出,要实现这样一个系统,数据采集是一个非常重要的方面。为了节约成本和提高DSP芯片的利用率,在这个系统中,一片DSP要承担16个通道的运算。从数据采集的角度来说,由于通道同时对应着终端和交换机两端,故DSP需要高速采集32个通道的数据。另外,高速ADC的出现和DSP性能的不断提高也对系统将来的升级提出了要求。所以对数据采集部分来说,高速、可扩展性是两个非常重要的指标。实现的系统就是以这两个指标为指导的。

目前的高速多通道数据采集系统一般有以下几种实现方法:一是直接采用高速的多通道模/数转换芯片,这些芯片有专门设计的与DSP接口的部分,但是这些芯片一般价格都非常昂贵;二是直接用FPGA完成整个的采集过程,这将耗费FPGA巨大的资源;三是DSP和模/数转换芯片的地址以及数据总线直接相接,通过单片机控制转换等过程,这种方法虽然便宜,但是可扩展性太差。综上所述,提出一种通过CPLD实现接口,将模拟转换通道映射到DSP的I/O设备空间甚至内存空间的方法。这种方法大大提高了DSP可以访问的外设数目;同时由于DSP不直接与模/数转换模块接口,所以ADC芯片的升级或者替代都不会影响原来的数据采集;而且采用了时分复用方式读取转换完成的数据,因此这个系统数据采集速率可以达到所采用的ADC芯片输出的速率。

DSP虽然在算法处理上功能很强大,但其控制功能是非常弱的;而CPLD本身并不具有内部寄存器,虽然可以用CPLD的逻辑块来实现寄存器,但是这将耗费大量的CPLD资源。然而,CPLD的强项在于时序和逻辑控制。本文介绍的多路数据采集系统就是充分利用了DSP和CPLD的优点,将多个A/D转换单元通过CPLD映射到DSP的I/O地址空间,利用CPLD屏蔽A/D转换的初始化以及读写操作过程,使得DSP可以透过CPLD这?quot;黑匣子"快速、准确地获取数据。

1 数据采集系统框架

整个数据采集系统主要由DSP处理模块、CPLD接口模块和ADC阵列三个部分组成,如图1所示。透过这样一个结构,DSP可以在未知ADC的控制方式的情况下,定时地以访问外设的方式来获得总共32个通道的模/数转换后的数据。

这样的系统框图只是完成了一个完整的数据采集功能,至于数据的处理以及DSP需要完成的其它功能,此图并未涉及。但对于一个DSP系统来说,数据采集在硬件中占据了很大的比重,这也符合DSP芯片应用的原则:用软件完成大部分的数字处理算法。

|

2 各功能模块的实现

2.1 ADC阵列的实现

此数据采集系统的设计目标是完成32路信号的采样,并且要求每路的采样率为50kHz。所以,这样一个系统达到的整体采样率为32×50k=1.6MHz。

在模/数转换环节,采用的A/D芯片一片可以同时完成4路转换。为了达到设计目标,需要8片这样的芯片。但是,如果直接将8片模/数转换芯片的数据总线全部连接起来输入到CPLD中或者将CPLD出来的某条控制信号线直接连接到8片芯片上,那么在驱动上就会出现问题。基于此种考虑,此系统将8片芯片分成两组,每组4片,然后从CPLD中引出两组数据总线以及两组控制总线分别对它们实现控制。这样就能很好地解决芯片的驱动问题。图2就是其中一组芯片的连接架构图。

|

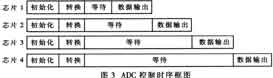

从这个架构图可以看出,这4片A/D转换芯片除了片选控制信号以外,其它的数据总线以及控制总线全部是分别连在一起的。将片选控制与其它控制分开的原因在于:芯片的初始化以及转换过程需要同时完成,但是转换后数据的输出则分别完成。ADC控制时序框图如图3所示。

|

要实现这样的控制时序,各个阶段对芯片的片选控制如下:在初始化阶段,所有A/D芯片的片选信号有效,此时可以对每片芯片写入相同的模式选择信号,同时启动采样脉冲和转换脉冲;在转换阶段,所有片选信号全部无效,此时芯片本身在内部完成模/数转换,同时将转换完成的数据放置在芯片内部的寄存器中;在数据输出阶段,首先是片芯片的片选有效,此时若有一个脉冲下降沿到A/D芯片的RD端口,则芯片1的转换完成,路数据将浮出到数据总线上,而其它芯片由于片选信号无效,虽然有RD输入也不会有数据输出,不会造成总线冲突。对于芯片1而言,接下来的几个RD脉冲可以分别使得转换完成后的几路数据浮现在数据总线上。芯片1的数据全部输出完成后,片选1无效,此时可使芯片2的片选信号有效。依此类推,就可以完成4片芯片的转换及数据输出。

2.2 CPLD接口模块的实现

整个CPLD接口模块实际上就是一片ALTERA公司的7000系列的CPLD(外部时钟电路除外),它控制ADC模块的初始化,同时接收并分析DSP过来的I/O端口读取信号,为DSP和ADC之间搭起一个通道。

在DSP要求读取数据时,CPLD将DSP过来的IOSTROBE作为A/D芯片的RD信号,同时对I/O地址总线的第3位至第5位译码产生A/D芯片的片选信号,这样只要是地址按照每次递增1的方式读取数据,就可以使得8片A/D分时片选有效,完全符合上面提到的读取数据的要求。另外,还依靠位地址确定CPLD到DSP的数据输出总线是否定义成高阻态来避免总线冲突。

由于A/D芯片是采用5V供电的,所以其输出高电平将高于DSP输入高电平所能承受的范围。解决这个问题的方法之一是采用降压芯片(比如LVT系列)用3.3V供电,3.3V供电可以承受5V的输入,同时输出也和3.3V兼容,但是这种方法需要单独外接几片LVT芯片,占据宝贵的PCB板空间;方法之二是给CPLD芯片提供双电源,其中提供给I/O脚的电源为3.3V,此时输入电压可以和5V及3.3V系统兼容,同时输出电压高电平可以达到3.3V,符合A/D芯片高电平电压2.4V的要求。所以,数据总线通过CPLD到DSP实际上是因为电平转换的需要。

2.3 DSP处理模块

DSP处理模块在硬件电路上是非常简单的,主要由一片DSP芯片、一片EEPROM以及一片介于这两者之间的用作电平转换的LVT系列的芯片组成。

DSP通过地址总线可以区分访问的模拟通道的标号。需要注意的是:由于采用的A/D芯片是通过对RD脉冲信号计数来确定访问的是同一片芯片内部4路中的哪一路,所以实际上地址总线的低两位是没有选择功能的,对一片A/D芯片访问时,两位地址一定要从00开始递增到11,否则所读取的数据就是乱的。例如,转换完成后的DSP若想越过前两个通道来获得第3个通道的数据,它必须给出两个读取I/O端口的指令,紧接着这两个指令后的读取端口指令才可以获得第3个通道的有效数据。

当然,可以通过CPLD首先将所有转换完成的数据缓存下来,然后分析I/O地址来将对应的通道的数据浮现到数据总线上。这样做使得DSP可以自由地选择需要访问的通道,但需要比较大的缓存,利用CPLD作缓存是非常不经济的。

3 仿真和调试

本系统的软件开发主要包括两部分,一是DSP读取I/O口的程序,二是CPLD的时序控制程序。前一程序的开发采用的是TI公司的CCS开发环境,并且利用DSP内部的BOOTLOADER在起电时将存储在外挂EPROM中的程序装载进DSP的程序空间。而后一程序的开发采用的是ALTERA公司的MAXPLUSII,利用这个环境,完成了程序的编制、仿真以及时序分析,并在找出关键路径的基础上优化了整个芯片的内部延时。

在调试的过程中,利用DSP提供的JTAG接口实时地观察采集进来的数据。当对32路模拟通道分别提供不同频率的正弦信号时,可以看到相对应的通道的数字信号也按照固定的频率来变化,并且各个通路不存在串扰的情况。经过测试获得本系统的各种参数如下: 单路模拟信号采样率:5kHz

系统模拟信号采样率:50kHz×32=1.6MHz

单个采样点读取时间:80ns(受ADC芯片的限制)

DSP(5402)单指令周期:10ns

DSP读取数据占用资源:((80÷10)×1.6×106)÷106

=12.8mips

CPLD使用I/O口: 48

CPLD使用Logic cells:80

由此说明这样一个系统达到1.6MHz的采样率时工作是稳定可靠的。

本系统的设计思想和方法不仅适用于多路数据采集,而且能有效地扩展DSP访问外设的能力。实践证明,这种系统在成本控制、可扩展性以及资源利用效率上都有非常大的提高。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。