|

摘 要: 介绍了用单片机实现数字相位变换器(又称脉冲调相器)的一种设计方法。主要描述了数字相位变换器的工作原理,基于AT89C2051单片机的硬件电路的工作原理以及软件设计的基本思想和程序设计方法。

|

|

数字相位变换器又称脉冲调相器,是鉴相型位置伺服系统中的主要控制线路。它的作用是将脉冲信号转换为相位变化信号。在传统的系统设计中,脉冲调相器是通过纯硬件线路实现的,线路复杂、设计难度大、调试难度也较大。作者在旋转变压器鉴相型位置检测系统中设计脉冲调相器时,改变传统的纯硬件设计方法,采用单片机实现脉冲调相,使硬件设计工作大大简化,易于实现,且电路调试简便。

|

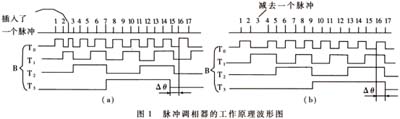

| 1 脉冲调相器的工作原理 用一个频率为fcp的时钟脉冲去触发一个容量为M的计数器时,如用四位二进制计数器,其容量为16,那么在计数器的输出端可获得一个频率为1/16fcp的方波信号。如果在时钟脉冲触发计数器的过程中,向计数器加入一个额外的脉冲,则由于计数器提前完成16个数的计数任务,而使得的输出提前翻转,从而使计数器的输出产生了一个正的相移Δθ,如图1(a)所示。同理,在时钟脉冲触发计数器的过程中,如果扣除一个脉冲,则由于计数器推迟完成16个数的计数任务而使的输出延时翻转,从而导致其输出产生一个负的相移Δθ,如图1(b)。 |

|

|

Δθ与计数器容量有关,即Δθ=360°/M。如果在时钟脉冲触发计数器的过程中,向计数器加入或扣除的不止是一个脉冲,而是N个脉冲,则计数器输出相移θ=NΔθ。

|

| 2 硬件电路 硬件电路如图2所示。 |

|

| 2.1 电路实现的功能 (1)产生两个频率为80kHz的异步时钟脉冲信号FA和FB; (2)在时钟脉冲FA的反相信号作为计数脉冲触发容量为200的计数器过程中,控制FB的反相信号插入计数脉冲,使计数器输出信号相位前移;或阻塞进入计数器,即扣除脉冲,使计数器输出信号相位后移。 2.2 工作原理 频率为160kHz的时钟脉冲源CP160K经二分频器U1A分频后产生两个频率为80kHz的方波信号Q和。Q和再分别与CP160K作与运算,由门U3A和U4A分别输出获得两个频率为80kHz的异步脉冲信号和FB,波形如图3所示。 |

|

| 无调相指令时,89C2051单片机将输出位P1.2和P1.3均置成0。此时门U5A被打开,门U3B被封锁并输出1,打开门U4B,计数脉冲系列通过U4B触发容量为100的计数器U6计数,在二分频器U1B的第9脚输出400Hz方波信号。当单片机接收到正调相指令时,将P1.2置为0,P1.3置为1,门U5A打开,通过门U5A,此时U3B也打开,FB通过门U3B变成,并和同时进入门U4B,形成计数脉冲系列。由于FA和FB是异步信号,因此达到了在计数脉冲系列中插入脉冲的目的,使计数器U6A多计一个数,从而使二分频器U1B输出信号相位前移,工作波形如图4a所示。 |

|

|

当单片机接收到负调相指令时,将P1.2置为1,P1.3置为0。此时门U5A被封锁并输出1,时钟脉冲被阻塞,同时门U3B被封锁并输出1,时钟脉冲FB也被阻塞,达到了在计数脉冲系列中减去脉冲的目的,使计数器U6A少计一个数,从而使U1B输出信号相位后移,波形如图4b所示。

|

| 3 软件设计 程序设计的主要思路是:执行正方向调相时,根据给定的脉冲数(假设脉冲数为N),控制P1.3的状态,实现插入N个的操作,参见图4(a);执行负方向调相时,根据给定的脉冲数N,控制P1.2的状态,实现阻塞N个的操作,参见图4b 。程序框图如图5所示,程序清单见程序1和程序2,其中寄存器B中存放给定脉冲数N。 |

|

| 程序1:正方向调相程序 MA6: MOV A,B JZ MA4 MA7: JB P1.6 $ JNB P1.6 $ NOP SETB P1.3 JB P3.1 $ JNB P3.1 $ CLR P1.3 DJNZ B MA7 MA4 RET 程序2: 负方向调相程序

|

|

参考文献 4. AT89C2051 datasheet https://www.dzsc.com/datasheet/AT89C2051_810086.html. |

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。