| 摘 要 PCI9052是PLX技术公司开发的PCI协议从模式接口芯片。介绍了其功能、特点及应用,并说明了其引脚功能及配置注意事项。给出了一个开关控制器电路实例,旨在介绍如何利用PCI9052完成由ISA扩展板向PCI扩展板的转换。 关键词: PCI ISA 扩展板 PCI9052 |

| PCI(Peripheral Component Interconnect,即外围部件互连)总线是一种能为主CPU及外设提供高性能数据总线的局部总线。1992年以INTEL为首的多家集团开始设计PCI总线,其V2.0规范于1993年4月正式发布。PCI总线具有严格的规范,这就保证了它具有良好的兼容性,符合PCI规范的扩展卡可插入任何PCI系统可靠地工作;PCI总线可以提供极高的数据传送速率(132MB/S);PCI总线与CPU无关,与时钟频率亦无关,可适用于各种平台,支持多处理器和并发工作;PCI总线还具有良好的扩展性,通过PCI-PCI桥路,可允许无限地扩展;PCI总线以它的即插即用特性取代了VESA局部总线。一个PCI接口包括一系列的寄存器,这些寄存器中的信息允许计算机自动地配置PCI卡。PCI总线是目前PC机上的一种总线。 PCI总线协议非常复杂。如果开发PCI扩展板使用可编程逻辑阵列芯片来完成PCI协议的执行,其工作量和难度都是巨大的,一般都会选用PCI专用接口芯片。下面介绍PCI9052接口芯片。 |

|

1 PCI9052芯片介绍 1.1 主要特点 |

|

| (9) 四个局部片选信号。9052提供了四个局部片选信号,基地址和每一个片选的范围可由串行EEPROM或主控制器独立编程 (10)五个局部地址空间。基地址和每一个局部地址空间的范围可由串行EEPROM或主控制器独立编程。 (11)读/写存储延时和写周期保持。对于ISA总线,读/写信号可以从时钟周期的开始延时。 (12)局部总线等待状态。附加的LRDYi握手信号用于产生各种等待状态,9052有内部等待状态发生器。 (13) 可编程预锁存计数器。局部总线预锁存计数器可以编程为0(无预锁存),4、8、16或连续值(预锁存计数器关闭)模式。 |

|

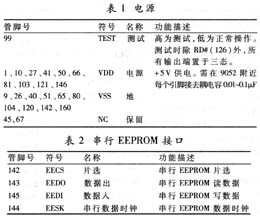

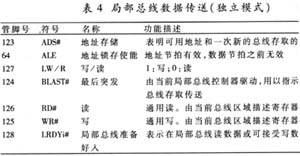

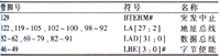

| 1.2 引脚功能 PCI9052为160脚塑封PQFP封装结构。其各管脚功能按功能块划分分别列于表1~表7中。 |

|

|

|

2 PCI9052芯片的使用 PCI9052接口芯片作为通用PCI接口,其应用场合和范围是广泛的。随着PC机中ISA扩展槽数量的逐渐减少直至取消,PCI扩展槽已成为PC机主板配置的主流,今后的扩展板的开发必定是基于PCI接口的。 但现行的很多ISA接口的扩展板,尤其是自己自主研制的具有某些特殊功能的扩展板,如何使之能在PCI槽上继续使用,显得很有意义。下面就着重介绍PCI9052接口芯片将ISA扩展板直接转换为PCI扩展板的应用。 |

| 2.1 ISA接口模式介绍 PCI9052的内部结构中包含了一个独立的ISA逻辑接口,通过这个逻辑接口可以完成由ISA到PCI的平滑转换。它支持8位和16位数据宽度的ISA设备,该设备可以是内存映射,也可以是I/O映射。先读模式用于提高读取数据的吞吐量。一旦ISA接口模式使能,PCI9052只执行单个周期操作。特别指出的是,串行EEPROM必需使ISA接口模式使能。 |

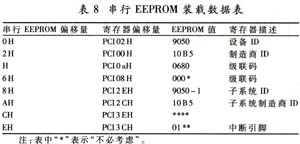

| 2.1.1 配置方法 可以使用两种方法配置PCI9052用于ISA接口模式。 方法一:烧写串行EEPROM方法。使用烧写器,将数据写入串行EEPROM,参照表8使用恰当的数据。需要注意的是,对于ISA模式,LRESET#(132)引脚必须始终为高电平,并确认MODE(68)引脚置为0,处于非复用模式。 |

|

| 方法二:热配置方法。从PCI总线通过PCI9052芯片使用方法一的相同数据来烧写串行EEPROM。该方法需要注意的是,LRESET#(132)引脚的极性在ISA模式时由低变为高,并确认MODE(68)引脚置为0。 |

| 2.1.2 配置注意事项 当为ISA接口模式配置时必须注意以下几点: ①存取ISA接口引脚时要参照PCI9052引脚的C/ISA模式引脚图来连线。 ②空间0分配给ISA接口的内存存取。 ③空间1分配给ISA接口的I/O存取。 ④无论空间0的局部地址处于CS0#范围还是空间1的局部地址处于CS1#范围,ISA存取均有效。 ⑤标准的从周期可以使用空间2、空间3和串行EEPROM来存取。 |

| 2.2 应用实例 下面给出一个电子转换开关控制器应用实例。该控制器的功能是,当检测到触发条件时,便向端口200H送一个控制码C0H,用以控制继电器完成开关动作。该例子旨在说明如何将PCI9052用于ISA扩展板向PCI扩展板的转换。 |

| 2.2.1 硬件设计 控制器硬件电路结构图如图1所示。 电路分为三部分。部分是9052与PCI插槽间的连接信号线。这些信号包括地址数据复用信号AD31:0,总线命令信号C/BE3:0#和PCI协议控制信号PAR、FRAME#、IRDY#、TRDY#、STOP#、IDSEL、DEVSEL#、PERR#、SERR#。第二部分是与串行EEPROM的连线。这里有四根信号线:EESK、EEDO、EEDI和EECS,串行EEPROM的数据可以提前用烧写器烧好,也可以在线烧写。第三部分是9052与应用电路的连接。在本例中主要用到的是ISA局部总线信号,有数据线LAD7:0,地址线ISAA1:0、LA23:2,I/O读写信号线IOWR#、IORD#,地址锁存BALE。 2.2.2 软件设计 程序分为两部分,一部分为PCI9052各配置寄存器赋值并初始化芯片,另一部分为主程序,任务是不断查询注册表中的相关键值,一旦条件满足,即向端口送控制码。程序用DELPHI语言完成。选用DELPHI的 |

| 主要原因是可编译成独立的可执行文件,不带任何动态连接库,程序短小精悍,并且DELPHI各版本间的兼容性比较好。程序流程图如图2所示。 |

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。