1 步进电机的控制原理

步进电机是数字控制电机,它将脉冲信号转变成角位移,即给一个脉冲信号,步进电机就转动一个角度,因此非常适合对数字系统的控制。步进电机可分为反应式步进电机(简称“VR”)、永磁式步进电机(简称“PM”)和混合式步进电机(简称“HB”)。

步进电机区别于其他控制电机的特点是,通过输入脉冲信号来进行控制,即电机的总转动角度由输入脉冲数决定,而电机的转速由脉冲信号频率决定。

步进电机的驱动电路根据控制信号工作,控制信号由各类控制器来产生。其基本原理作用如下:

① 控制换相顺序,通电换相。这一过程称为“脉冲分配”。例如:四相步进电机的单四拍工作方式,其各相通电顺序为A—B—C—D。通电控制脉冲必须严格按照这一顺序分别控制A、B、C、D相的通断,控制步进电机的转向。如果给定工作方式正序换相通电,则步进电机正转;如果按反序换相通电,则电机就反转。

② 控制步进电机的速度。如果给步进电机发一个控制脉冲,它就转一步,再发一个脉冲,它会再转一步。两个脉冲的间隔越短,步进电机就转得越快。调整控制器发出的脉冲频率,就可以对步进电机进行调速。

2 控制器的总体设计

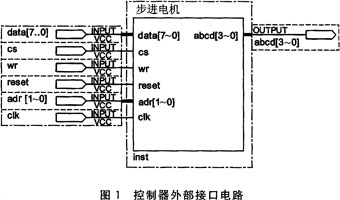

控制器的外部接口电路如图1所示。各引脚的功能如下:

data[7~0] 控制器与单片机等设备的总线接口;

cs片选信号,低电平有效;

wr写信号,低电平有效;

reset复位信号,低电平有效;

adr[1~0] 内部寄存器地址信号,与单片机等设备地址线相连;

clk待分频的时钟,可由FPGA提供;

abcd[3~0] 四相位输出。

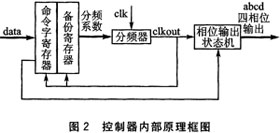

控制器的内部原理框图如图2所示,由命令字寄存器(Cmd_reg)、分频系数备份寄存器(fp_back)、分频器、相位输出状态机组成。

其中命令字寄存器(Cmd_reg组成如下(对应的地址为“00”):

X未用位。

Ini 对控制器初始化为1时有效。当该位为1时,备份寄存器的数据直接装入分频器的寄存器reg_data[15~0],装入后由硬件自动置0。

New 当对正在运行的控制器写入新的分频系数时,对该位置1;当下一个分频器输出的clkout时钟来到时,将fp_back写入到reg_data[15~0]中,分频器便按新的分频系数进行分频。

Manner[1~0] 电动机的驱动方式,用来控制相位输出状态机的输出,“00”表示单四拍方式,四相位输出为(A—B—C—D);“01”表示双四拍,四相位输出为(AB—BC—CD—DA),八拍(A—AB—B—BC—C—CD—D—DA)。

分频系数备份寄存器(fp_back) 两字节寄存器,reg_data[15~0]为分频器的一个16位寄存器,接收fp_back的值,对系统的分频为2~65 536。对于12 MHz的输入频率,分频后频率为6 MHz~183 Hz,(本设计中,步进电机的启动转速、转距、加速度由使用者根据实际情况自己计算)分频后每个clkout走一个步距角。对于步距角为1.8°的电机,可以满足各种速度的要求。

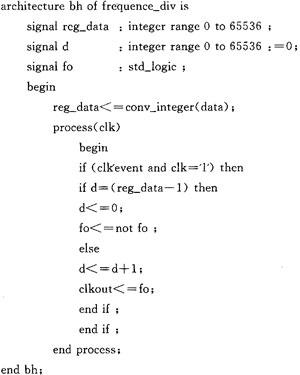

3 分频器的设计

分频器是该控制器实现的关键,在这里作为一个独立的模块,data[15~0]为分频系数。系统时钟Clk被分频系数寄存器中值分频后,输出Clkout作为相位输出状态机的时钟,每个Clkout到来时,产生相位转换,步进电机运行一个步距角。分频器的程序如下:

图3所示为3分频时单四拍的输出仿真图。

结 语

本文的创新点为将该步进电机控制器的控制字和分频系数映射在主控制器(DSP或单片机等)的内存空间,控制时仅需对其进行写操作,使步进电机的控制变得简单方便;而且,可节省主控制器(DSP或单片机等)的外围资源,减少板上负载。系统中可以加入电机运行总步数控制寄存器及其电路、加速度寄存器及其控制电路等,打造一个更智能的步进电机控制器。

[1]. CPLD datasheet https://www.dzsc.com/datasheet/CPLD_1136600.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。