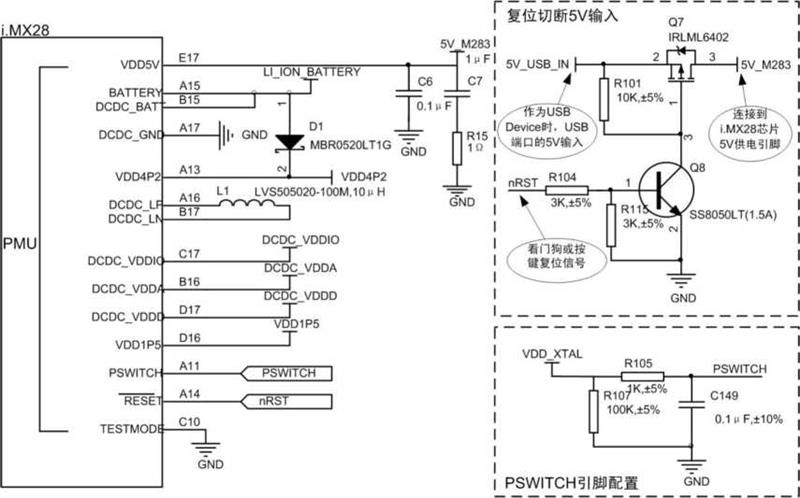

对于i.MX28系列处理器,不同的供电方式硬件设计和软件配置都有所不同。 EasyARM-i.MX283(7)A默认采用如图4-13所示的

电池供电应用方案。

BATTERY、DCDC_BAT引脚连接4.2V电源输入,该4.2V电路如图4-6所示。DC-DC转

换器3路输出电压共用一个电感L1,电感量根据具体应用及产品来确定,为延长电池寿命,电 感直流阻抗尽量低,同时应确保电感能承受的峰值电流大于可能流过的电流。Freescale官 方推荐电感值4.7^H~15阳。为保证输出电压稳定,DC-DC输出三路电压的去耦电容至少33pF。 DCDC_BATT和VDD4P2之间接肖特基

二极管,保证供电电源切换过程中输出电压稳定。 PSWITCH引脚配置为上电启动PMU的DC-DC

转换器。

当使用USB Device功能时,外部USB Host设备提供的5V电源需要接入VDD5V,以使USB Device功能正常,如果此时系统需要复位,仍然要切断外部USB Host设备提供的5V电源。

图4-13 i.MX28电源电路

4.5

存储器电路设计

NAND Flash 电路设计

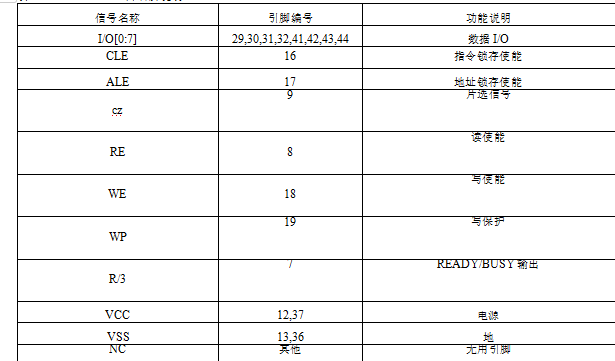

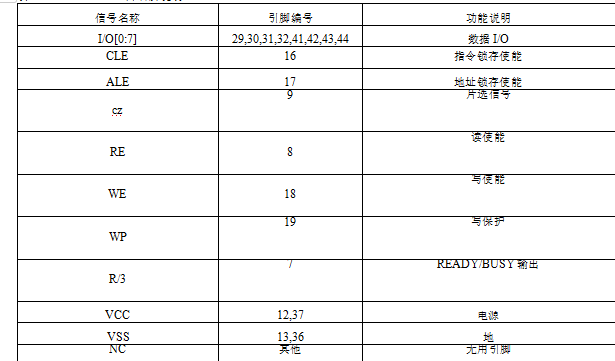

为了能够方便存储系统文件,使用用户程序、数据能掉电保存,EasyARM-i.MX283(7)A上 配置了容量128MB的NAND Flash,型号是MXIC (旺宏)的MX30LF1G08AA-TI,管脚说明 见表4.2。i.MX28内置的NAND Flash控制器支持8bit数据宽度,I/O速度达50MB/s,并有独立的片选信号。

表4.2 NAND Flash芯片管脚说明

信号名称引脚编号功能说明

I/O[0:7]29,30,31,32,41,42,43,44数据I/O

CLE16指令锁存使能

ALE17地址锁存使能

cz9片选信号

RE8读使能

WE18写使能

WP19写保护

R/37READY/BUSY 输出

VCC12,37电源

VSS13,36地

NC其他无用引脚

NAND电路设计

如图4-14所示。NAND Flash所需的3.3V电源由处理器PMU提供。亜通过10K电阻下拉到地,确保在上下电及空闲状态时不会对芯片进行误写、误擦除操作。在通过 10K电阻上拉到Vcc,使芯片在上下电及空闲状态时失能,以免发生误操作。LED用于指示程序是否运行正常。而f通过10K电阻下拉到地,确保芯片在上、下电时处于保护状态。

复位脉冲200ms;

看门狗定时器:1.6s溢出周期;

的电源电压检测。

WDI是看门狗输入引脚,连接到CPU的GPIO0_21,该GPIO0_21引脚需要在0.8s内进行电平反转,否则看门狗定时器将会溢出,_将输出低电平。M是手动复位输入引脚,低电平有效。

图4-16中将看门狗输出引脚兩而与手动复位输入引脚只瓦通过电阻接到一起,当看门狗定时器溢出时,M输入低电平,屈T引脚将会输出200ms的低电平复位脉冲,从而引起CPU复位。C20、C113这两个电容起滤波作用,一个放CAT706旁,一个放CPU复位引脚旁,能极 大地提高EMC性能。

如果在程序开发阶段,需要禁止看门狗功能,可以将WDO_EN信号连接到3.3V(即跳线 帽短接JP4),此时看门狗电路就算没有喂狗信号也不会输出复位信号。

注:EasyARM-i.MX283(7)A 原理图中 nRST_OUT 和 nRST 是同一个信号。

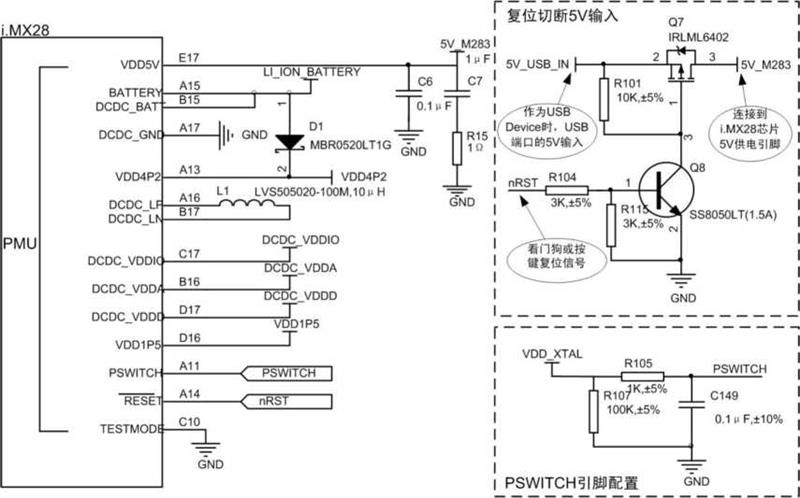

4.6.2按键复位及5V关断电路

处理器供电方式不同时,相应的复位电路也有所不同。仅采用4.2V供电时,只需在CPU 复位引脚上产生一个100ms的低电平即可。需要使用USB Device功能时,还要将USB Device 的VBUS信号连接到处理器的VDD_5V引脚,处理器检测到VDD_5V引脚上有5V电压后 Device功能才能正常使用。而当处理器的VDD_5V引脚上有5V电源时,复位过程还需要将该 5V电源断开,才能保证系统复位正常。因此,在需要使用USB Device功能时, EasyARM-i.MX283(7)A的复位电路除了给出复位信号外,还需要完成对输入5V的关断,如图

4-17所示。

nRST_IN连接到复位芯片(CAT706)的手动复位输入引脚,nRST_OUT是CAT706的复 位输出信号,USB_OTG_VBUS_IN是USB Device的接口电源,默认不与系统的5V电源连接, USB_OTG_VBUS 连接到 CPU 的 VDD_5V 弓丨脚。

系统正常工作时,nRST_OUT输出高电平,Q8导通。当EasyARM-i.MX283(7)A不作为 USB Device设备时,USB_OTG_VBUS和VDD_5V都是0V,此时只需给CPU的复位引脚产生100ms以上的低电平就可以正常复位;当作为USB Device设备使用时,Q7导通,处理器的 VDD_5V引脚上有5V电源。当按下复位按键时,nRST_IN变低,CAT706的复位输出信号 (nRST_OUT)输出200ms的低电平给CPU复位引脚,同时还控制Q7、Q8断开,切断连接到 CPU VDD_5V引脚的USB_OTG_VBUS电源,从而保证系统复位正常。

只有当系统作为USB Device设备或处理器采用4.2V和5V供电方案时,才需要针对CPU VDD_5V引脚的5V关断电路;不作为USB Device设备或仅采用4.2V供电时,5V关断电路可以不焊接。

注:USBOTG当作USBDevice使用时,处理器的5V电源引脚需要检测到5V电源,才可以作为Device正常工作。