摘 要:本文介绍了基于FPGA的自带移相信号源的相位测量仪的设计。在系统设计中研究了DDS信号源的FPGA实现方法。经过验证,系统结构简单,运行可靠。

关键词:DDS;FPGA;VHDL;相位测量

引言

随着集成电路的发展,利用大规模集成电路来完成各种高速、高电子仪器的设计已经成为一种行之有效的方法。采用这种技术制成的电子仪器电路结构简单、性能可靠、测量且易于调试。本文采用Altera CycloneII系列FPGA器件EP2C5,设计了高相位测量仪。测量相位差所需的信号源在FPGA内部运用DDS原理生成,然后通过高速时钟脉冲计算两路正弦波过零点之间的距离,通过一定的运算电路得到终相位值,测相为1°。

图1 相位测量仪硬件结构图

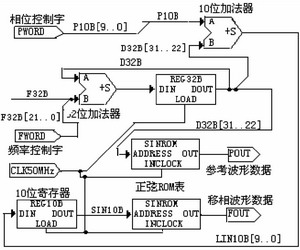

图2 基于DDS的数字移相信号发生模块框图

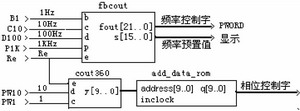

图3 控制模块顶层原理框图

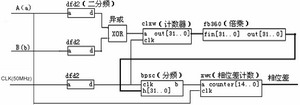

图4 相位测量模块原理框图

系统硬件设计

该基于FPGA的相位测量仪,硬件组成包括FPGA、高速DAC以及电压比较器等部分。其系统硬件结构如图1所示。

该测量仪由按键来预置正弦波的频率及相位。通过FPGA内部的控制模块来计算并产生正弦波所需的频率控制字和相位控制字,然后将控制字输入DDS模块以产生波形数据输出,经10位高速DAC THS5651输出两路正弦波。在测相位差时,将图1中移相正弦波输出分为两路,其中一路直接经电压比较器LM311整形后输入测相模块;另外一路先通过被测电路,然后再经电压比较器整形后输入测相模块,从而得到正弦波经被测电路后产生的相移。

基于FPGA的硬件电路设计

DDS移相信号源设计

DDS的基本原理是利用采样定理,通过查表法产生波形,本系统的移相信号发生模块如图2所示。

图2中,加法器与寄存器级联构成相位累加器。通过时钟脉冲触发相位累加器,从而将频率控制字不断累加。相位累加器产生溢出,就完成周期性的动作,这个周期就是DDS合成信号的一个频率周期。

用相位累加器输出的数据作为波形存储器的相位取样地址,把存储在波形存储器内的波形抽样值经查找表查出,从而完成相位到幅值的转换。然后将波形存储器的输出送到DAC,通过DAC将数字量形式的波形幅值转换成合成频率的模拟波形。

图2中FWORD是10位频率控制字;PWORD是10位相移控制字,用来控制正弦信号输出的相移量;SINROM用来存放正弦波数据,有10位数据线和10位地址线。其中数据文件是MIF文件(数据深度1024,数据类型为10进制数),可由Matlab生成,存放数据的单元采用定制ROM的方法生成;POUT和FOUT都为10位输出,分别和两个高速DAC THS5651相连。

控制模块的生成

在产生波形的过程中,DDS模块所需的频率和相位控制字由在FPGA内部编写的控制模块来给定。控制模块的顶层原理框图如图3所示。

图3中,B1、C10、D100、P1K分别为频率步进输入端;Re为复位端;PW1、PW10分别为1 10南辔徊浇淙搿F渲衒bcout为频率控制字计算模块,完成由频率步进值到二进制频率控制字的转换。

cout360为相位输入计算模块,由相位输入端的脉冲输入计算出实际的移相值(0麀359 )。add_data_rom是存放相位控制字的ROM,其数据文件是MIF文件,内部360个地址值分别对应0麀359南辔 ,每个地址中的数据为每个相位值对应的正弦波ROM的地址值。由于正弦波ROM将一个波形分成了1024个点,则0麀359南辔恢刀杂α薙INROM中的360个点。考虑到1024/360=2.84非整,为了减小移相误差,提高移相,本设计中采用分段处理的方法,将360个地址分成60组。第15、30、45、60组的6个地址中点与点之间的距离都为3;其余各组前5点之间的点距为3,第5点与第6点之间的点距为2。

相位测量模块设计原理

本系统的相位测量采用由高速时钟脉冲测量两路波形过零点之间距离的方法。相位测量模块原理框图如图4所示。

图4中,A、B为两路方波输入,CLK为50MHz时钟输入,dfd2块为下降沿触发的2分频模块。A、B经2分频的目的是使测相范围由0麀180┐蟮 0麀360OR为异或门,其输出信号的脉宽为(b-a)。clxw为一高速计数器,通过25MHz的高频时钟来计算(b-a)的长度。fb360模块为倍乘模块,主要完成(b-a)×360的运算。bpsc模块为分频模块,将25MHz的时钟信号进行(b-a)×360倍的分频,使其输出信号脉宽为Tclk×(b-a)×360(Tclk为25MHz的时钟周期)。xwc为相位差计数模块,通过A相输入脉冲,计算Tclk×(b-a) ×360的长度,然后完成(b-a)×360/a的计算,进而得出相位差值输出,同时该模块还将测得的相位差值送到数码管显示。

在对该模块进行仿真时,人为设定了频率为10KHz,相位差为72

系统验证调试

在整个系统的验证中,由外部按键通过控制模块来设定波形的频率和相位值,并通过将DDS模块的输出端FOUT和POUT外接10位DAC THS5651来产生波形。通过在示波器观察两路波形发现,波形比较稳定,频率与设定值一致。此外,为了测量DDS模块产生的移相是否正确,还人为的通过相位输入端设定相移值,并将参考波形输出端和移相输出端输出的波形经整形后,用测相模块测量两路波形的相位差,通过硬件调试发现测得的相位差与设定的相位差完全一致,从而证明了该系统是、稳定的。

结语

本系统选用Altera公司的quartusII4.1作为硬件开发平台,并采用VHDL语言进行电路设计。在设计中按功能划分模块,方便了调试与修改,且易于升级。同时,系统设计中还较多采用了同步时序电路来实现各个进程模块的功能,从而有效避免了电路毛刺现象。此外,在相位测量模块中,相位差计数块还带有锁存功能,从而有利于输出的相位差值显示稳定。

[1]. EP2C5 datasheet https://www.dzsc.com/datasheet/EP2C5_1438349.html.

[2]. LM311 datasheet https://www.dzsc.com/datasheet/LM311_451347.html.

[3]. MIF datasheet https://www.dzsc.com/datasheet/MIF_2043409.html.

[4]. C10 datasheet https://www.dzsc.com/datasheet/C10_1842564.html.

[5]. D100 datasheet https://www.dzsc.com/datasheet/D100_2060604.html.

[6]. dfd2 datasheet https://www.dzsc.com/datasheet/dfd2_1397887.html.

[7]. 25MHz datasheet https://www.dzsc.com/datasheet/25MHz_1136611.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。