A/D 转换器即模数转换器,或简称 ADC,通常是指一个将模拟信号转变为数字信号的电子元件。 通常的模数转换器是将一个输入电压信号转换为一个输出的数字信号。由于数字信号本身不具有实际意义,仅仅表示一个相对大小。故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为的可转换信号大小。而输出的数字量则表示输入信号相对于参考信号的大小。 模数转换器最重要的参数是转换的精度,通常用输出的数字信号的位数的多少表示。转换器能够准确输出的数字信号的位数越多,表示转换器能够分辨输入信号的能力越强,转换器的性能也就越好。

下面简要介绍常用的几种类型的基本原理及特点:积分型、逐次逼近型、并行比较型/串并行型、∑-Δ调制型、电容阵列逐次比较型及压频变换型。

1)积分型(如TLC7135)

积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。

2)压频变换型(如AD650)

压频变换型(Voltage-Frequency Converter)是通过间接转换方式实现模数转换的。其原理是首先将输入的模拟信号转换成频率,然后用计数器将频率转换成数字量。从理论上讲这种AD的分辨率几乎可以无限增加,只要采样的时间能够满足输出频率分辨率要求的累积脉冲个数的宽度。其优点是分辩率高、功耗低、价格低,但是需要外部计数电路共同完成AD转换。

3)并行比较型/串并行比较型(如TLC5510)

并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。

串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。还有分成三步或多步实现AD转换的叫做分级(Multistep/Subrangling)型AD,而从转换时序角度又可称为流水线(Pipelined)型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。这类AD速度比逐次比较型高,电路规模比并行型小。

4)∑-Δ(Sigma?/FONT>delta)调制型(如AD7705)

∑-Δ型AD由积分器、比较器、1位DA转换器和数字滤波器等组成。原理上近似于积分型,将输入电压转换成时间(脉冲宽度)信号,用数字滤波器处理后得到数字值。电路的数字部分基本上容易单片化,因此容易做到高分辨率。主要用于音频和测量。

5)电容阵列逐次比较型

电容阵列逐次比较型AD在内置DA转换器中采用电容矩阵方式,也可称为电荷再分配型。一般的电阻阵列DA转换器中多数电阻的值必须一致,在单芯片上生成高精度的电阻并不容易。如果用电容阵列取代电阻阵列,可以用低廉成本制成高精度单片AD转换器。最近的逐次比较型AD转换器大多为电容阵列式的。

6)逐次比较型(如TLC0831)

逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。其电路规模属于中等。其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

AD转换器的主要指标如下。

(1)分辨率(Resolution)。指数字量变化一个最小量时模拟信号的变化量,定义为满刻度与2n的比值。分辨率又称精度,通常以数字信号的位数来表示。

(2)转换速率(Conversion Rate)。是指完成一次从模拟转换到数字的AD转换所需的时间的倒数。积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级属中速AD,全并行/串并行型AD可达到纳秒级。采样时间则是另外一个概念,是指两次转换的间隔。为了保证转换的正确完成,采样速率(Sample Rate)必须小于或等于转换速率。因此习惯上将转换速率在数值上等同于采样速率也是可以接受的。常用单位是Ksps和Msps,表示每秒采样千/百万次(Kilo / Million Samples Per Second)。

(3)量化误差(Quantizing Error)。由于AD的有限分辨率而引起的误差,即有限分辨率AD的阶梯状转移特性曲线与无限分辨率AD(理想AD)的转移特性曲线(直线)之间的偏差。通常是1个或半个最小数字量的模拟变化量,表示为1LSB、1/2LSB。

(4)偏移误差(Offset Error)。输人信号为雷时输出信号不为零的值,可外接电位器调至最小。

(5)满刻度误差(Full Scale Error)。满刻度输出时对应的输人信号与理想输人信号值之差。

(6)线性度(Lineafity)。实际转换器的转移函数与理想直线的偏移,不包括以上3种误差。

AD的其他指标还有精度(Absolute Accuracy)、相对精度(Relative Accuracy)、微分非线性、单调性和无错码、总谐波失真(THD,Total Harmonic Distotortion)和积分非线性等。

对于AD转换器,选取的标准主要决定于采样频率和位数,以及价格、供货周期、应用情况等其他因数。生产高速AD的主要厂家有AD公司、Maxim公司以及TI公司(也就是BB公司)。这三家公司在高速AD上的产品种类不是很多,根据对各种AD芯片的查阅,选择TI公司的AD转换芯片ADS5422。

ADS5422是14bit的采样频率可达62Msps的高速AD转换芯片,采用单- 5V电源供电,在采样频率为10M时其动态范围为82dB,信噪比达到72dB,其数字量输出可以直接和5V或者3.3V的CMOS芯片连接,模拟量输入的峰峰值为4V,可以直接输人0.5~4.5V的模拟量,封装形式为64脚的扁平四方封装,目前TI的官方报价为29美元/片(一次购买千片以上的单价)。国内也有该芯片出售,国内价格在300元左右。

14bit的AD转换适应信号的范围为10lg(214)dB=42dB,基本上可以适应各种应用场合。ADS5422的采样频率的大小由其输人时钟决定,输入时钟的范围可以在16ns~1μs,输人时钟为16ns时对应采样频率为62MHz,AD可以接受3V或者5V的TTL或者CM0S电平。DSP可以提供该时钟信号,并且可以软件设置输人时钟的各种特征量,包括时钟频率、高电平宽度等,基本上可以满足AD5422对时钟信号的要求。这里确定AD的实际采样频率为60MHz。这样,一秒钟内采样的数据量为50M个,由于DSP系统无法及时处理这些数据,在数据处理之前,必须将这些数据保存起来,使用ΠFO保存1M个数据,也就是20ms内的采样数据,1M个数据采集结束开始信号处理。由于高速AD采样导致信号不稳定,甚至出现错误。将设计多层板,加强布线的合理性,从电路板上尽可能去除干扰;其次提高算法的效率,节省计算时间。

和ADS5422功能接近的其他型号的AD还有AD公司的AD9244。和ADS5422相比,两者数据位数都是14bit,在信噪比上两者相近,时钟输入和操作方法相近,电源都是5V,输出数字信号都可以和3.3V的芯片兼容;其主要优点是功耗是ADS5422的一半,500mW;其主要缺点是输人模拟电压峰峰值为ADS5422的一半,只有2V。

AD公司其他的高速AD芯片还有AD6644,为其早期产品,操作方法和ADS5422、AD9244不一样,AD6644功耗达到1.3W。和AD9244相比,没有什么优点,AD9244是其替代产品。

高速AD的另外一个厂家Maxim公司也有一批高速AD产品,但采样频率在40MHz以上没有14bit数据的AD,其产品优势主要集中在中速AD上。

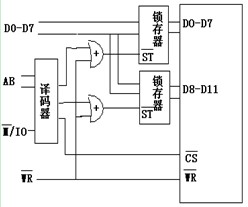

1、数据端口的设计

由于输出端口为输出口,所以在数据端口的设计时要遵守输出要锁存的设计原则,但对于D/A转换器内部具有锁存器时,可以直接与数据总线相连。

数据端口的设计应考虑D/A 转换器的内部结构和分辨率,目前常见的D/A转换器有:8位,10位、12 位,16位,当分辨率大于总线宽度时,需要增加外部数据锁存器,确保数据的同步。

MOV AX,N

OUT PORT1,AL

OUT PORT2,AH

OUT PORT3,AL

2、输出周期设定

可用软件定时或硬件定时中断的方法实现输出周期的控制。

D/A转换器是计算机或其它数字系统与模拟量控制对象之间联系的桥梁,它的任务是将离散的数字信号转换为连续变化的模拟信号。在工业控制领域中,D/A转换器是不可缺少的重要组成部分。

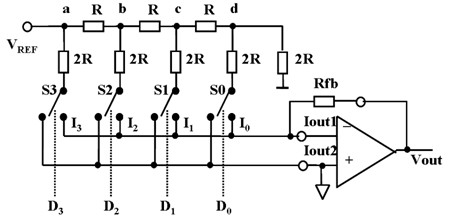

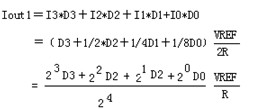

以下以一个四位的D/A转换器说明D/A转换器的工作原理:

当D3=1 I3=Vd/2R=VREF/(1×2R)

当D3=0 I3=0

当D2=1 I2=Vd/2R=VREF/(2×2R)

当D2=0 I2=0

当D1=1 I1=Vd/2R=VREF/(4×2R)

当D1=1 I1=0

当D0=1 I0=Vd/2R=VREF/(8×2R)

当D0=1 I0=0

Vout=-Iout1×Rf

由此可见:随着D3-D0的取值(0、1)的不同在运放输出端可以得到不同的电压量。如果用数字量来控制电子开关的通断(1表示接通,0表示断开)

例如:D3D2D1D0 VOUT

0000 0V

0001 1/24VREF*Rf/R

0010 2/24 VREF*Rf/R

0011 3/24 VREF*Rf/R

15/24 VREF*Rf/R

可见:在输出端可得到与输入数字量成正比的模拟电压量。