J-K触发器该是几种典型触发器中的一种,它通过J、K端的信号来控制其状态变换规律,用一句话来概括就是:其在CP下降沿前接受信息,在下降沿触发翻转,在下降沿后触发器被封锁。

1、电路结构

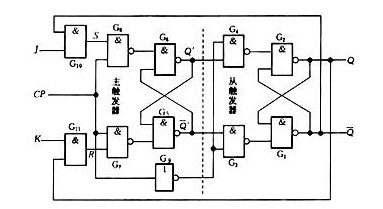

主从JK 触发器是在主从RS触发器的基础上组成的,如下图所示。 在主从RS触发器的R端和S端分别增加一个两输入端的与门G11和G10,将Q端和输入端经与门输出为原S端,输入端称为J端,将Q端与输入端经与门输出为原R端,输入端称为K端。

2、状态方程

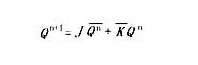

主从JK 触发器的状态方程为:

3、工作原理

由上面的电路可得到S=JQ,R=KQ。代入主从RS触发器的特征方程得到,当:

J=1,K=0时,Qn+1=1;

J=0,K=1时,Qn+1=0;

J=K=0时,Qn+1=Qn;

J=K=1时,Qn+1=-Qn(Qn非);

由以上分析,主从JK 触发器没有约束条件。在J=K=1时,每输入一个时钟脉冲,触发器翻转一次。触发器的这种工作状态称为计数状态,由触发器翻转的次数可以计算出输入时钟脉冲的个数。

脉冲工作特性:

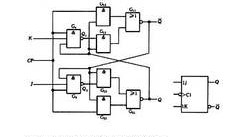

该触发器无一次变化现象,输入信号可在CP 触发沿由1变0时刻前加入。由图可知,该电路要求J、K信号先于CP 信号触发沿传输到G3、G4的输出端,为此它们的加入时间至少应比CP 的触发沿提前一级与非门的延迟时间,这段时间称为建立时间test。

输入信号在负跳变触发沿来到后就不必保持,原因在于即使原来的J、K信号变化,还要经一级与非门的延迟才能传输到G3和G4的输出端,在此之前,触发器已由G12、G13、G22、G23的输出状态和触发器原先的状态决定翻转。所以这种触发器要求输入信号的维持时间极短,从而具有很高的抗干扰能力,且因缩短tCPH 可提高工作速度。

从负跳变触发沿到触发器输出状态稳定,也需要一定的延迟时间tCPL。显然,该延迟时间应大于两级与或非门的延迟时间。即tCPL大于2.8tpd。

1.边沿JK 触发器具有置位、复位、保持(记忆)和计数功能;

2.边沿JK 触发器属于脉冲触发方式,触发翻转只在时钟脉冲的负跳变沿发生;

3.由于接收输入信号的工作在CP下降沿前完成,在下降沿触发翻转,在下降沿后触发器被封锁,所以不存在一次变化的现象,抗干扰性能好,工作速度快。

1.CP=0时,触发器处于一个稳态。

CP为0时,G3、G4被封锁,不论J、K为何种状态,Q3、Q4均为1,另一方面,G12、G22也被CP封锁,因而由与或非门组成的触发器处于一个稳定状态,使输出Q、Q状态不变。

2.CP由0变1时,触发器不翻转,为接收输入信号作准备。

设触发器原状态为Q=0,Q=1。当CP由0变1时,有两个信号通道影响触发器的输出状态,一个是G12和G22打开,直接影响触发器的输出,另一个是G4和G3打开,再经G13和G23影响触发器的状态。前一个通道只经一级与门,而后一个通道则要经一级与非门和一级与门,显然CP的跳变经前者影响输出比经后者要快得多。在CP由0变1时,G22的输出首先由0变1,这时无论G23为何种状态(即无论J、K为何状态),都使Q仍为0。由于Q同时连接G12和G13的输入端,因此它们的输出均为0,使G11的输出Q=1,触发器的状态不变。CP由0变1后,打开G3和G4,为接收输入信号J、K作好准备。

3.CP 由1变0时触发器翻转

设输入信号J=1、K=0,则Q3=0、Q4=1,G13和G23的输出均为0。当CP 下降沿到来时,G22的输出由1变0,则有Q=1,使G13输出为1,Q=0,触发器翻转。虽然CP变0后,G3、G4、G12和G22封锁,Q3=Q4=1,但由于与非门的延迟时间比与门长(在制造工艺上予以保证),因此Q3和Q4这一新状态的稳定是在触发器翻转之后。由此可知,该触发器在CP下降沿触发翻转,CP一旦到0电平,则将触发器封锁,处于1所分析的情况。