倍频器是使输出信号频率等于输入信号频率整数倍的电路。利用非线性电路产生高次谐波或者利用频率控制回路都可以构成它。输入频率为f1,则输出频率为f0=nf1,系数n为任意正整数,称倍频次数。它有很多种,包括晶体管倍频器、变容二极管倍频器等等

倍频器实质上就是一种输出信号等于输入信号频率整数倍的电路,常用的是二倍频和三倍频器。在手持移动电话中倍频器的主要作用是为了提升载波信号的频率,使之工作于对应的信道;同时经倍频处理后,调频信号的频偏也可成倍提高,即提高了调频调制的灵敏度,这样可降低对调制信号的放大要求。采作倍频器的另一个好处是:可以使载波主振荡器与高频放大器隔离,减小高频寄生耦合,有得于减少高频自激现象的产生,提高整机工作稳定性。

微波倍频器是一种基本的微波电路。所谓倍频器 是指能完成输入信号频率倍增功能的电子设备。原则 上,非线性器件都能实现倍频,而利用半导体器件的 非线性实现的倍频,即称为固态倍频器。当用一个正 弦信号激励非线性器件时,便会在基频的谐波频率上 产生功率。倍频电路的作用就是有效提取其中所需要 的谐波信号,而将其基频和不需的谐波加以抑制。

倍频器按其工作原理又可分为两大类:一种是非 线性电阻倍频。这类倍频器是利用双结型晶体管、场 效应晶体管或二极管的非线性电阻效应把大幅度正弦 倍频器的原理波变成电流脉冲,再用选频回路将所需要的谐波选出,以完成倍频作用。

另一种非线性电抗倍频,亦称为“参量倍频”。

其一是利用PN 结或金属一半导体结电容的非线性变化得到输入信号的谐波,经滤波器选出需要的频率.变容二极管倍频器、阶跃二极管倍频器以及利用集电极非线性效应做成的三极管倍频器都是非线性电容构成的倍频器;其二是利用非线性电感构成的倍频器。例如利用雪崩二极管雪崩渡越效应引起的非线性电感实现的倍频。

目前,在频率较低、倍频次数不是很高的场合,人们常采用晶体管有源倍频来实现 而在频率较高时往往采用变容二极管或是阶跃恢复二极管等无源电路。随着截止 频率很高的各种场效应管的出现,人们对利用场效应管的非线性来实现次数较低的倍频电路表现出极大的兴趣。

利用ADS射频仿真软件和嵌入法对倍频器的环境阻抗、有效激励电平进行了研究,针对倍频器输出端外加负载后对倍频效率产生的影响,提出了改进方法并进行了实际验证。

1 引言

众所周知,在用倍频链实现高频、高稳微波振荡源的过程中,倍频器倍频效率的高低不仅对简化电路和保持电路稳定性影响较大,而且对整个电路杂散、谐波的抑制都起着重要作用。传统的设计过程需要复杂的理论推导、大量的试验验证,或者依赖于经验进行设计而在现实工程应用中,有时却需要一些特殊的倍频器,如频率不是很常用,倍频次数又较高,采用外协加工,成本和时间都不划算等。对于这些既没有相关的工程设计经验,又无法获得倍频三极管器件完整的物理参数的情况,探索一个能快速有效设计出高性能倍频产品的方法就显得十分有必要了。在ADS射频仿真软件的帮助下,以AT42086(三极管)5倍频器(将114.8MHz倍到574MHz)为例,可以较完整地研究各种外围条件对倍频效率的影响。

2 仿真方法

当把倍频器单独看成为嵌入式器件时,在某个三极管的特定静态工作点下,倍频器两端的输入阻抗特性、输入端的激励电平对倍频效率都呈现出一种特殊的规律(比如说倍频器的激励电平并不是越高越好,有时高的激励电平反倒比低电平激励时产生的谐波幅度低)。因此,如何确定正确的直流工作点、输出端LC谐振回路和有效的激励电平是设计中面临的关键问题。鉴于这种情况,设计时可以充分利用现代射频设计工具来进行仿真以加快研发过程并设计出性能较好的倍频产品。

利用ADS仿真软件中相应的功能模块SmZ1、SmZ1(注意:SmZ1、SmZ2模块输出的是共轭值,由于设计时应该赋给倍频电路真值以模拟真实环境,所以要将结果取共轭),可以比较容易地处理仿真时电路外围环境阻抗问题,对于倍频的前级(比如放大电路),可以在软件中先建立放大电路原理图,然后设置SmZ1模块(测得输出阻抗,也就是倍频器输入的环境阻抗)并运行仿真以得到结果。同理,还应对倍频的后级电路做类似处理以得到倍频输出端的环境阻抗。这里所讲的后级电路一般是指带通滤波电路,对于大部分外购的滤波器,其输入、输出端口都要求在50Ω匹配条件下,因此,可以把50Ω假设成倍频器的输出环境阻抗直接带入倍频电路进行仿真。但这样的问题是:实际滤波器的滤波特性是在50Ω匹配的环境下测得的,而并不一定是它的输入输出端口就正好是50Ω,特别是对带通滤波器,其端口一般呈容性,而在调试修正电路里还应考虑如何在保证仿真有效性的前提下,对其进行端口的失配现象进行补偿。

利用嵌入法的设计思路是:把倍频电路本身看成一功能单元,其工作时的外围环境阻抗可以由输入输出两端的负载来指定。另外,为了便于观察激励电平的影响,可选用ADS中单音频率源作为输入端(该源也可人为指定环境阻抗)。倍频电路可按照三极管倍频经典电路搭建。图1所示是其倍频仿真电路原理图。在图1中,对于LC回路,由于倍频电路中LC回路器件可以有很多不同的组合,因此,它的选择也颇有讲究,具体的做法除可以参考相关文献外,也可以用ADS上的电路优化功能,来让软件来选择一组较为合适的取值。

本设计是以两端50Ω环境阻抗为例进行的,若具体情况不是50Ω或含有虚部,可以双击终端模块直接修改输出阻抗值的大小。格式为:(50+j*24)Ω。

在此虽然用的是很简单的电路模型,但是,这并不影响利用ADS对倍频特性进行仿真。

3 仿真实验及结果验证

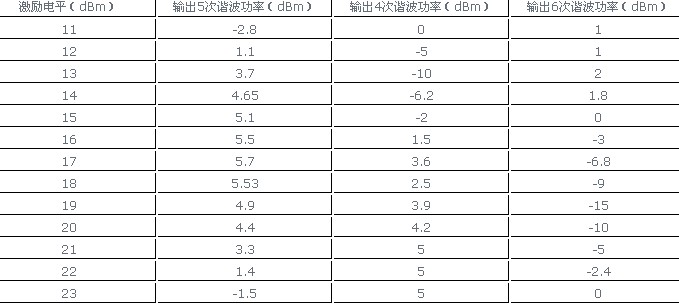

让软件进行多次的仿真实验,可以使设计人员通过生成的实验数据在很短时间内找到合适的输入激励电平。表1是笔者截取的一段数据。由于主要关心五次谐波,所以,为了便于观察,将其制成表格,并将其邻近的四、六次谐波也列了出来。

表1 不同激励电平时的谐波功率值

从谐波分析结果图表上可清楚的看到:当激励电平为17dBm的时,三极管AT42086的倍频效率是的(见图2),为5.727dBm。而在其邻近的其它电平激励下,倍频后的5次谐波输出都相对低一些。

通过研究倍频器的倍频效率对激励电平的变化规律,可为确定输入激励电平的大小提供依据。不仅如此,在计算整个电路系统电平分配时,也可以把倍频器件的有效激励电平作为基点来折算出其它器件的工作电平值。

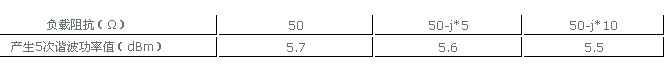

实际实现时,作为射频电路,即便原理上已经设计的很好了,但由于电路工作频率很高,实际电路板如果设计不好,就有可能导致信号波长和结构的物理参数发生变化,从而使电路出现自激、谐波抑制不好,波形失真、信号功率下降等现象。这里设计的倍频器是一种对环境阻抗很敏感的器件。由于一般从电路设计上,都希望用尽量少的器件来实现功能。本电路输出级元件少到只有LC谐振回路,因此一方面符合最小化设计要求,另一方面,输出级又很容易受到负载的牵引而使倍频效率降低。对此,可以通过ADS软件实验来分析这个现象。表2给出了两例5次谐波的功率值。实际上,针对倍频器的特点可以对这些“失配”提出一套切实可行的“修正”办法。当然,合理正确的仿真是能够快速有效实现修正的先决条件。

倍频器的输入级一般是放大器或者放大器加衰减网络,故前级的输出阻抗是不好确定的,可能是容性,也可能是感性。也就是说,修正倍频器输入端的环境阻抗比较困难,对此,可以把主要矛盾放到输出级去。因为两端口器件的S参数不仅和本级有关,还和输出级的匹配情况有关,在失配不是很严重的情况下,可以通过改善输出级的匹配来同时修正两个端口的匹配。为了实现倍频器的倍频功能,可以在输出端加带通滤波器以选出所需要的谐波信号。而设计良好的带通滤波器的输入端的端口一般都呈容性(如果不是,就意味着在DC附近还有一个通带,这种情况很少见),因此可以在实际电路调试中把倍频器输出级与下面带通滤波器连接的隔直电容(也就是图1中的C4)取下来,而换用电感来抵偿滤波器端口的容性效应。笔者在实际调试中尝试过两种替代方法,而且都取得了很好的效果:一种是用贴片电感,其优点是一致性好,适合批量加工。缺点是由于器件取值的离散性,因此在首次调试时需要拿很多不同值的电感焊到板子上试,而且也不容易取到值;另一种是用漆包线的线绕线圈,特点是可以用镊子进行连续的电感值调试,容易取到值,但这种方法的缺点是每件都需要手调,难于用在大规模的生产上。

表2 不同负载下5次谐波的功率值

笔者将C4换成线绕电感线圈后,实际调出的倍频结果是5次谐波输出功率大于软件仿真得出的数值,即用线圈进行无间断的电感值调协可以弥补倍频电路中器件取值离散而难以得到倍频结果的缺点,从而得到比软件仿真还要好的谐波输出功率。笔者的实际试验结果是:四次谐波:5.5955dBm,五次谐波:6.559dBm,六次谐波:-1.226dBm。

4 小结

本文以一个具体的例子着重讲述了如何利用现代射频仿真工具ADS来优化倍频器的设计过程,同时针对软件仿真与实际电路的客观差距提出了一套行之有效的解决方案,并通过实际验证使理论仿真和实际实现得到了良好的吻合。实践证明:通过对ADS软件设计过程的优化,可以提高工程开发效率,因而在人力、时间的投入上有着明显的优势。