图文详情

产品属性

相关推荐

74HC4053D

74HC4053D

74HC4053D

74HC4053D

General description

The 74HC4053; 74HCT4053 is a high-speed Si-gate CMOS device and is pin compatible

with the HEF4053B. It is specified in compliance with JEDEC standard no. 7A.

The 74HC4053; 74HCT4053 is triple 2-channel analog multiplexer/demultiplexer with a

common enable input (E). Each multiplexer/demultiplexer has two independent

inputs/outputs (nY0 and nY1), a common input/output (nZ) and three digital select

inputs (Sn). With E LOW, one of the two switches is selected (low-impedance ON-state)

by S1 to S3. With E HIGH, all switches are in the high-impedance OFF-state, independent

of S1 to S3.

VCC and GND are the supply voltage pins for the digital control inputs (S0 to S2, and E).

The VCC to GND ranges are 2.0 V to 10.0 V for 74HC4053 and 4.5 V to 5.5 V for

74HCT4053. The analog inputs/outputs (nY0 to nY1, and nZ) can swing between VCC as

a positive limit and VEE as a negative limit. VCC VEE may not exceed 10.0 V.

For operation as a digital multiplexer/demultiplexer, VEE is connected to GND (typically

ground).

2. Features and benefits

Wide analog input voltage range from 5 V to +5 V

Low ON resistance:

80 (typical) at VCC VEE = 4.5 V

70 (typical) at VCC VEE = 6.0 V

60 (typical) at VCC VEE = 9.0 V

Logic level translation: to enable 5 V logic to communicate with 5 V analog signals

Typical ‘break before make’ built-in

ESD protection:

HBM JESD22-A114F exceeds 2000 V

MM JESD22-A115-A exceeds 200 V

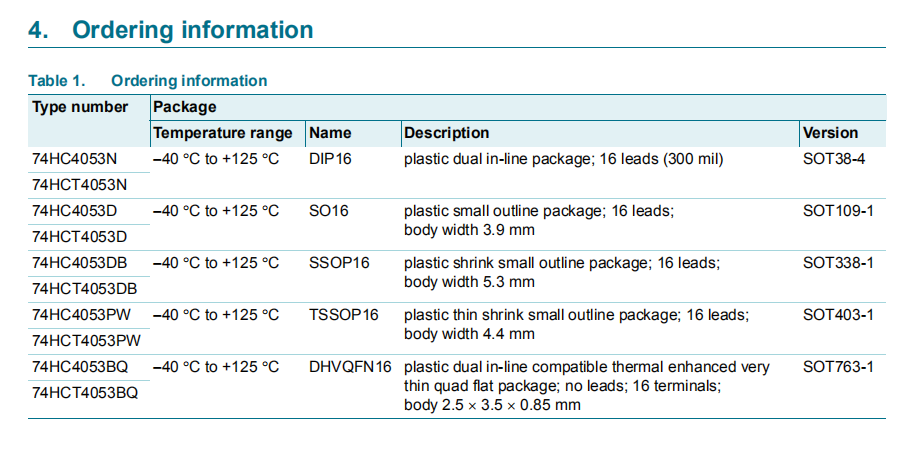

Multiple package options

Specified from 40 C to +85 C and 40 C to +125 C

3. Applications

Analog multiplexing and demultiplexing

Digital multiplexing and demultiplexing

Signal gating

74HC4053D

NXP

SOP

19+

环保

2000/盘

中国

黑色