图文详情

产品属性

相关推荐

74HC138D

FEATURES

• Demultiplexing capability

• Multiple input enable for easy expansion

• Ideal for memory chip select decoding

• Active LOW mutually exclusive outputs

• Output capability: standard

• ICC category: MSI

GENERAL DESCRIPTION

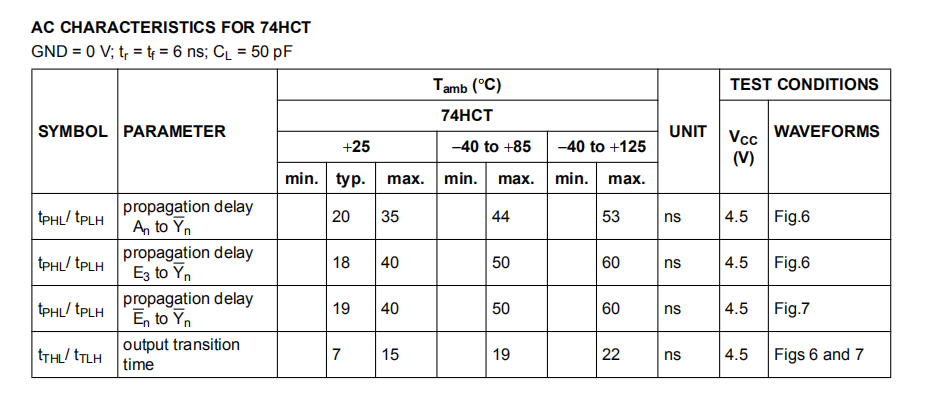

The 74HC/HCT138 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT138 decoders accept three binary

weighted address inputs (A0, A1, A2) and when enabled,

provide 8 mutually exclusive active LOW outputs (Y0 to

Y7).

The “138” features three enable inputs: two active LOW

(E1 and E2) and one active HIGH (E3). Every output will be

HIGH unless E1 and E2 are LOW and E3 is HIGH.

This multiple enable function allows easy parallel

expansion of the “138” to a 1-of-32 (5 lines to 32 lines)

decoder with just four “138” ICs and one inverter.

The ”138” can be used as an eight output demultiplexer by

using one of the active LOW enable inputs as the data

input and the remaining enable inputs as strobes. Unused

enable inputs must be permanently tied to their

74HC138D

appropriate active HIGH or LOW state.

The ”138” is identical to the “238” but has inverting outputs.

74HC138D

74HC138D.

74HC138D

NXP

SOP

19+

环保

2000/盘

中国

黑色