图文详情

产品属性

相关推荐

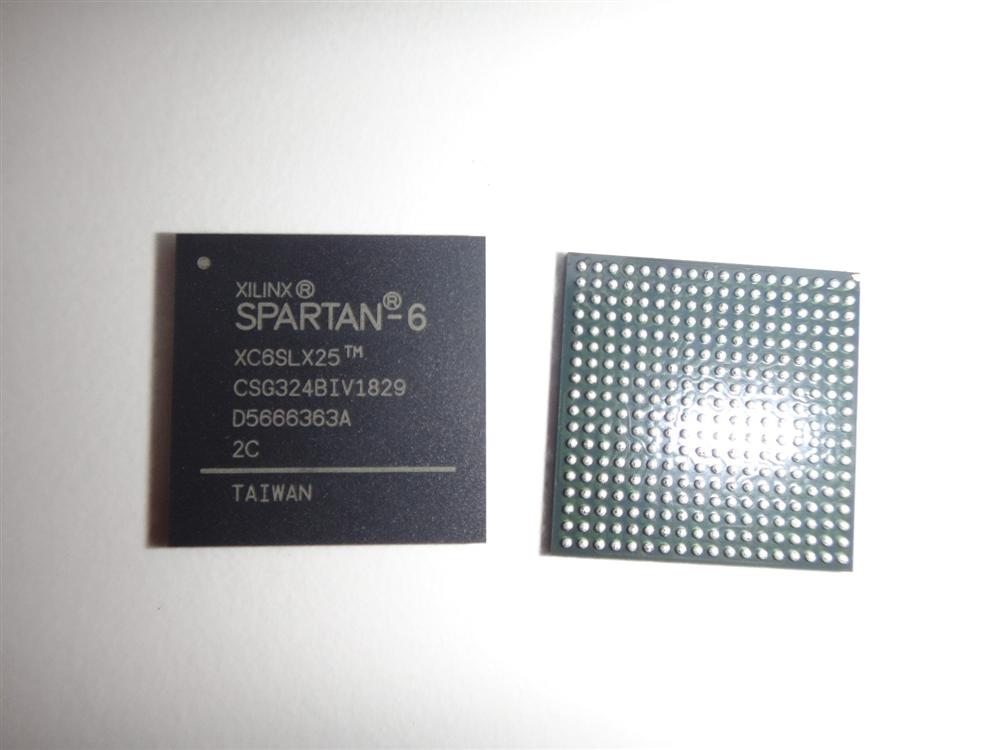

XC6SLX25-2CSG324现场可编程门阵列以zui低的总成本为大容量应用提供了ling先的系统集成能力,提供了从3840到147443个逻辑单元的扩展密度,基于成熟的45 nm低功耗铜缆工艺技术,提供了成本、功率和性能的zui佳平衡,提供一种新的、更高效的双寄存器6输入查找表(LUT)逻辑和丰富的内置系统级块选择。

XC6SLX25-2CSG324C包括18 Kb(2 x 9 Kb)的块RAM、第二代DSP48A1片、SDRAM内存控制器、增强的混合模式时钟管理块、SelectIO? 技术、功率优化的高速串行收发器块、gao级系统级电源管理模式、自动检测配置选项,以及通过AES和设备DNA保护增强的IP安全性。这些功能以前所未有的易用性为定制ASIC产品提供了一种低成本的可编程替代方案。

XC6SLX25-2CSG324C为大容量逻辑设计、面向消费者的DSP设计和成本敏感的嵌入式应用提供了zui佳解决方案,它是目标设计平台的可编程硅基础,提供集成软件和硬件组件,实现设计师在开发周期一开始就关注创新。

多电压、多标准选择? 接口银行

?每个差分输入/输出的数据传输速率高达1080 Mb/s

?可选输出驱动,每个引脚高达24 mA

?3.3V至1.2V输入/输出标准和协议

?低成本HSTL和SSTL内存接口

?热插拔合规性

?可调输入/输出转换速率,以提高信号完整性

?LXT FPGA中的高速GTP串行收发器

?高达3.2 Gb/s

?高速接口包括:串行ATA、Aurora、,

1G以太网、PCI Express、OBSAI、CPRI、EPON、,

GPON、DisplayPort和XAUI

?PCI Express设计的集成端点块(LXT)

?低成本PCI?技术支持,与

33 MHz、32位和64位规格。

?高效的DSP48A1切片

?高性能算法和信号处理

?快速18 x 18乘法器和48位累加器

?流水线和级联能力

?用于辅助滤波器应用的预加法器

?集成内存控制器块

?DDR、DDR2、DDR3和LPDDR支持

?数据速率高达800 Mb/s(12.8 Gb/s峰值带宽)

?具有独立FIFO的多端口总线结构,以减少

设计时间问题

?丰富的逻辑资源,逻辑容量增加

?可选移位寄存器或分布式RAM支持

?高效的6输入LUT提高了性能

zui小化功率

?具有双触发器的LUT,用于以管道为中心的应用

?具有广泛粒度的块RAM

?具有字节写入启用功能的快速块RAM

?18 Kb块,可选择编程为两个

独立9 Kb块RAM

?时钟管理磁贴(CMT)用于增强性能

?低噪音、灵活的时钟

?数字时钟管理器(DCM)消除了时钟偏差

和占空比失真

?用于低抖动时钟的锁相环(PLL)

?同时乘法频率合成,

除法和相移

?16个低偏差quan球时钟网络

设备包组合和zui大可用I/O

需要注意的是,XC6SLX25-2CSG324C与基本DCM功能无关,频率合成输出CLKFX和CLKFX180可以编程为生成任何输出频率,即DCM输入频率(FIN)乘以M,同时除以D,其中M可以是2到32之间的任何整数,D可以是1到32之间的任何整数。

zui后,如果需要采购或者查看更多XC6SLX25-2CSG324C器件参数信息,都可以联系我们。

XC6SLX25-2CSG324C

XILINX

BGA

2022+

1260