图文详情

产品属性

相关推荐

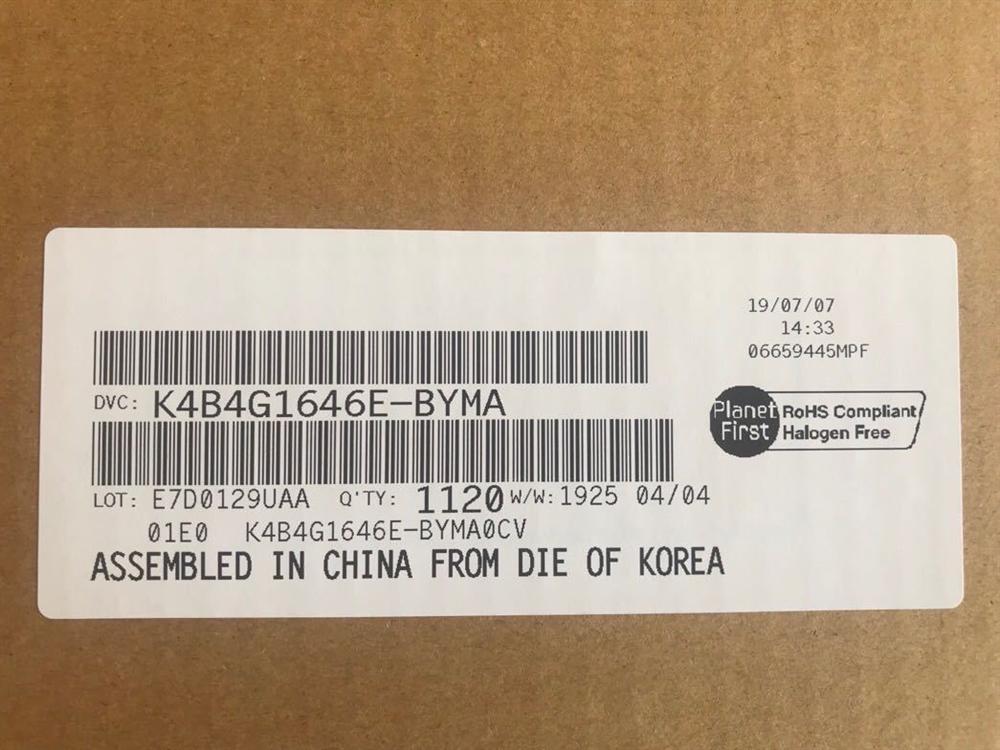

描述:K4B4G1646E-BYMA

具有无铅和无卤素的96FBGA(符合RoHS)

K4B4G1646E-BYMA

主要特点:

•JEDEC标准1.35V(1.28V〜1.45V)和1.5V(1.425V〜1.575V)

•VDDQ =

1.35V(1.28V〜1.45V)和1.5V(1.425V〜1.575V)

•400 MHz fCK表示800Mb / sec / pin,533MHz

fCK表示1066Mb / sec / pin,

667MHz fCK(用于1333Mb / sec / pin),800MHz fCK(用于1600Mb

/ sec / pin)

933MHz fCK for 1866Mb / sec /

pin

•8家银行

•可编程CAS延迟(已发布CAS):5,6,7,8,9,10,11,12,13

•可编程加性延迟:0,CL-2或CL-1时钟

•可编程CAS写入延迟(CWL)=

5(DDR3-800),6

(DDR3-1066),7(DDR3-1333),8(DDR3-1600)和9(DDR3-1866)

•8位预取

•突发长度:8、4,tCCD

=

4,不允许无缝读取

或撰写[使用A12或MRS即时down load]

•双向差分数据选通

•内部(自我)校准:通过ZQ引脚进行内部自我校准

(RZQ:240欧姆±1%)

•使用ODT引脚进行管芯端接

•平均刷新时间为7.8us(低于TCASE85C,3.9us低于TCASE)

85C<TCASE

<95C

•支持工业温度(-4095C)

--40°C≤TCASE≤85°C时的tREFI 7.8us

-85°C

<TCASE≤95°C时的tREFI

3.9us

•异步复位

•包装:96球FBGA-x16

•所有无铅产品均符合RoHS

•所有产品均无卤素4Gb DDR3 SDRAM

E-die被组织为32Mbit x 16I / Os x 8bank,

设备。该同步设备实现了高速双数据速率

一般应用的传输速率高达1866Mb /

sec / pin(DDR3-1866)。

该芯片的设计符合以下DDR3

SDRAM关键功能,例如发布的CAS,可编程CWL,内部(自)校准,

利用ODT引脚和异步复位来终止芯片。

所有控制和地址输入均与一对外部提供的差分时钟同步。输入在差分时钟的交叉点锁存(CK上升和CK下降)。所有I

/ O均与

源同步方式的一对双向选通(DQS和DQS)。地址总线用于传送行,列和库地址

RAS / CAS复用样式中的信息。

DDR3设备运行

使用单个1.35V(1.28V〜1.45V)或1.5V(1.425V〜1.575V)电源

和1.35V(1.28V〜1.45V)或1.5V(1.425V〜1.575V)VDDQ。

4Gb

DDR3L E-die器件可用于96ball FBGA(x16)。

K4B4G1646E-BYMA

K4B4G1646E-BYMA

SAMSUNG/三星

K4B4G1646E-BYMA

SDRAM

96FBGA

1866 Mbps

1.35 V

0~85°C

批量生产

100000