图文详情

产品属性

相关推荐

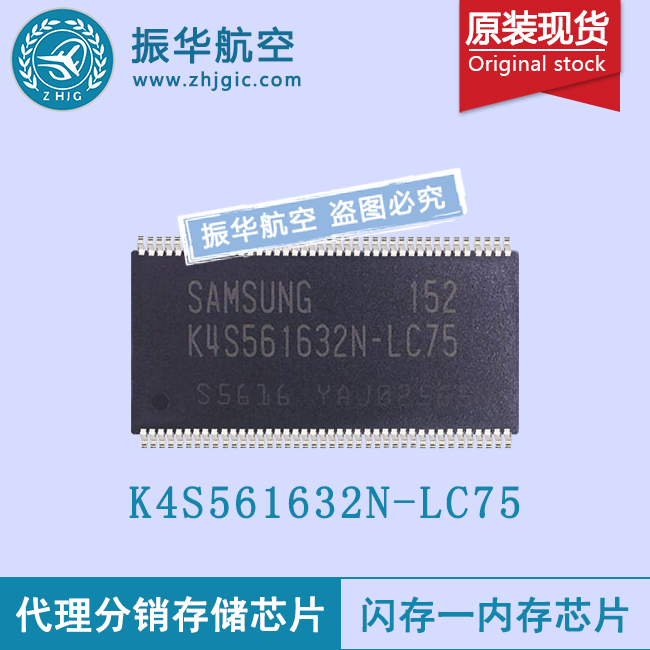

K4S561632N-LC75内存芯片商品质保证主图

K4S561632N-LC75内存芯片商品质保证参数

制造商IC编号K4S561632N-LC75

厂牌SAMSUNG/三星

IC 类别SDRAM

IC代码16MX16 SD

脚位/封装TSOP2

外包装

无铅/环保无铅/环保

电压(伏)3.3 V

温度规格0°C to +85°C

速度75 NS

标准包装数量

标准外箱

潜在应用LED APPLICATION/LED應用MP3 /MP4 /MP5 PLAYEROEM/ODM/TURNKEY/BUYING IC/组装代工廠/購買IC

K4S561632N-LC75内存芯片商品质保证相关信息

μPSD存储器的地址配置 μPSD中对存储器地址分配需遵守以下规则:

规则1.主/次FLASH块FS0~FS7,CSBOOT0~CSBOOT3的地址范围不能大于其物理尺寸;

规则2.主FLASH块FS0~FS7之间地址不能重叠;

规则3.次FLASH块CSBOOT0~CSBOOT3之间地址不能重叠;

规则4.SRAM、I/O、外设I/O地址不能重叠;

规则5.主FLASH,次FLASH和SRAM,I/O,外设I/O,若地址重叠,存储器有效优先级为SRAM、I/O、外设I/O最高,次FLASH次之,主FLASH。在PSDSOFT设计中,若违反规则2、3、4会出现错误,必须修改才能进行下一步;而违反规则1只会发出警告,如果忽略一定要小心。规则5属于解释型规则,不会提出任何提示,注意地址重叠情况下优先级低的存储器不能被访问。

μPSD中通过DPLD对每个存储器的地址进行分配,DPLD的结构如图2所示。图2 DPLD的结构DPLD包括“与”阵列和“或”阵列,“与”阵中有输入项共57项,“或”阵中有输出项共16项。输入项表示可参于地址译码的信号,输出项即每个存储器的CS信号。DPLD的输入项中最常用的是A0~A15,页寄存器PGR0~PGR7,#RD、#PSEN、#WR、ALE。PDN是在功率管理时使用,如果在地址中加入PDN,表示只有在电源有效时地址译码才有效,通常这项是自动加入的,使用者可不用管。DPLD的输入项和输出项不是必须全部配置的。在对μPSD的存储器进行地址配置时,一个最重要的原则是“不超过64KB就不要分页,没有使用到的块就不必配置”。对于小的项目中没有使用到所有存储器,不用去配置,这样既简单,减少出错,又方便调试和检查。除CSIOP是必须配置的外,其他项均可根据需要进行配置。PSEL由外设I/O模式控制,在PIO模式下,PA口的所有I/O被设置为三态、双向MCU数据缓冲器方式,与MCU的P0口有些类似。DPLD中必须声明PSEL0和/或PSEL1的有效地址范围,在访问此地址时,PA口进入PIO方式。

K4S561632N-LC75

SAMSUNG

BGA

17+

800mhz