在最近的IEDM上,三星电子(以下简称三星)在早前的IEDN上公布了超越DRAM小型化极限的技术,美光科技(以下简称美光)和台积电将公布提高非易失性存储器容量的技术。

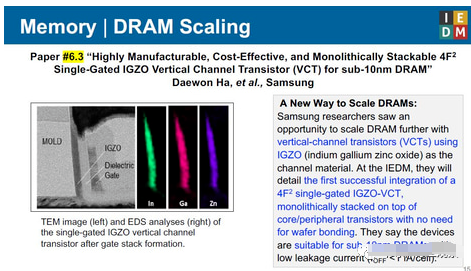

三星电子表示,已开发出适用于 10 纳米以下技术节点的垂直通道 DRAM 单元晶体管技术。使用氧化物半导体IGZO作为沟道材料。用于DRAM单元的垂直沟道晶体管单片集成在核心电路晶体管层和外围电路晶体管层上。

美光科技已原型设计出一款 32Gbit 大容量非易失性 RAM,由两层铁电存储单元堆叠阵列层(1T1C 型)组成。通过在 CMOS 外围电路区域顶部堆叠存储单元阵列来提高存储密度。

台积电开发了一种嵌入式存储器,其中STT-MRAM单元配置有一个选择器和一个磁隧道结(MTJ),并且单元阵列布置在交叉点上。使用 16 纳米和精细加工技术制作存储单元阵列原型。

有趣的是,三星和美光开发的存储技术都是通过在外围电路层之上放置存储单元阵列层来实现存储密度。两家公司都拥有使用类似技术(阵列下 CMOS)大规模生产 3D NAND 闪存的经验。在研发方面,有迹象表明将扩展到闪存以外的高密度存储器。

三星:推进DRAM 继续前进 今年年初,三星发布博客说,今年对三星来说特别有意义,因为它标志着其成为全球第一大 DRAM 供应商的第 30 周年,这一记录可以追溯到三星 1992 年开发 64Mb DRAM 时。

在接下来的几年里,三星将一如既往地通过颠覆性创新和扩展技术的进步,继续生产最高质量的 DRAM。

三星表示,DRAM 扩展从未如此困难。不过,三星已经在准备解决方案来克服 DRAM 面临的最大挑战。

随着DRAM尺寸降至10nm左右,工艺难度显着增加。尺寸越小,图案化、单元晶体管、单元电容和带宽要求提出的挑战就越大。为了克服这些挑战,三星一直在准备自己的微缩工艺和设备技术。它还一直在探索和开发新材料和新阵列架构的颠覆性解决方案。

三星的微缩工艺将继续发展,推动其 DRAM 路线图的进展。由于 High-NA,EUV 图案化将继续进步,这将使三星能够通过更小的工艺步骤增强其图案化能力。此外,还将引入电阻更低的新金属来缩小字线和位线。

采用这些新材料可以使字线和位线电阻分别提高40%和35%。这使得这些关键技术能够突破电池尺寸的极限。

具有更高 k 值和高深宽比接触蚀刻工艺的电介质对于引领 DRAM 电容器的下一阶段也至关重要。三星也为此做好了准备,并完全具备在亚纳米尺度上原子控制高 k 电介质结晶度的能力。使用 FinFET,三星可以在 0.9V 操作电压下将速度和功率分别提高 30% 和 20%。

您在这里看到的是三星最新的尖端 DRAM 产品,将于明年开始发布。其中包括三星用于数据中心和服务器的高容量 32Gb DDR5,它将支持高达 1TB 的模块。其低功耗移动DRAM和高性能图形DRAM将分别具有8.5Gbps和28Gbps的速度,使其成为世界上最快的。LLW DRAM(一种低延迟宽 IO 产品)以及提供 1TB/s 超高带宽的 HBM 也在开发中。

三星还提供广泛的定制 DRAM 解决方案,涵盖从缓存到大容量内存的所有内容。其中包括 LLC-DRAM,一种末级缓存 DRAM;HBM-PIM,具有内存处理功能的高带宽内存;AXDIMM,嵌入近数据处理的 DIMM;CXL-MXP,内存扩展器;CXL-PNM,一款具有新 CXL 接口处理功能的扩展器。

着眼于未来,三星不断探索 DRAM 技术的下一步发展,并开发实现这一未来所需的解决方案。凭借从传统 DRAM 到定制 DRAM 的创新,三星已准备好提供行业所需的 DRAM 解决方案。它将继续创新,坚信前进的道路在于接受更多的挑战、创新和合作。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。