而在当前的技术发展背景下,随着云技术的快速普及,以及物联网、人工智能和高性能边缘计算等新兴技术趋势的不断涌现,企业对系统的要求变得更为严苛,需要更快速、灵活的企业系统来高效管理工作负载。数据中心为了实现更高的数据吞吐量,采用了耗电量大的高速处理器,这使得每台依靠典型 12V 电源轨的服务器的电流电平提高至 250A 以上,同时还需要 20 至 30mF 的负载电容,以满足系统的瞬态负载分布要求。

在这样的高电流系统中,每台服务器前端的热插拔电路起着至关重要的作用。热插拔电路通常结合使用热插拔控制器和金属氧化物半导体场效应

晶体管(MOSFET),能够针对过载、输出短路等系统故障提供浪涌电流限制和保护。在系统出现故障时,热插拔控制器可将 MOSFET 保持在饱和区域,从而把故障电流限制在安全水平。然而,在设计可靠的热插拔电路时,由于系统电流不断上升且输出电容较大,而 MOSFET 处理功率应力的能力有限,这给设计带来了巨大的挑战。

传统的简化热插拔电路主要由热插拔控制器、外部电流检测

电阻器和功率 MOSFET 组成。当系统发生故障时,热插拔控制器会促使 MOSFET 在饱和区域工作,以此限制故障电流,但这会使 MOSFET 承受较大的漏源压降和很高的功率应力。

热插拔控制器通过可编程故障计时器(TTIMER)实现功率限制方案(PLIM),以此提供 FET 安全工作区域(SOA)保护。选择合适的 PLIM 和 TTIMER 值非常关键,这能确保所选的 MOSFET 在发生应力事件的工作温度下,仍能在其 SOA 限制内工作。若所选的 FET 在设计中不可行,就必须选择具有更高 SOA 的 FET,这使得热插拔电路设计变得高度迭代且复杂。

电子保险丝虽然具有集成的过热保护电路,可监测内部 FET 温度,并在 FET 承受较长时间应力时将其关断,以确保 FET 在 SOA 限制内工作。但目前电子保险丝器件只能在低电流下工作,所以要实现高电流电路保护,只能采用基于 FET 的外部热插拔解决方案。

为确保 FET 始终处于其 SOA 范围内,热插拔控制器会实施功率限制方案。当 FET 的功率损耗达到 PLIM 时,会触发故障计时器;若功率损耗未降至 PLIM 以下,将在 TTIMER 之后关断 FET。

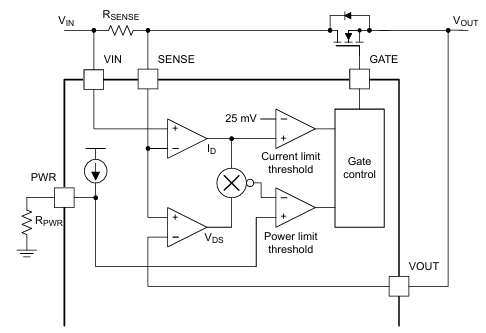

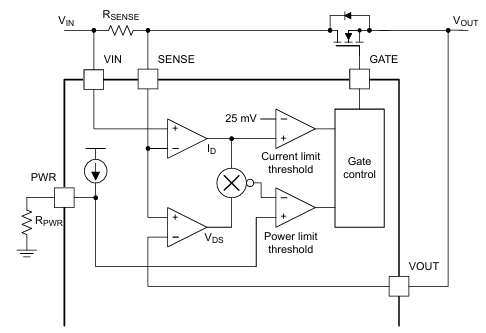

热插拔控制器的功率限制控制环路(如图 1 所示)包含电流检测放大器和电压

检测电路。电流检测放大器用于监测检测电阻的电压(VSNS)以获取电流信息,电压检测电路则用于测量 FET 的电压。将两者的输出相乘,可得到 FET 中的功率损耗。把该损耗值与和 PLIM 成比例的电压进行比较后,可调节栅极电压,确保 MOSFET 中的功率损耗始终低于 PLIM。

图 1:热插拔控制器中的功率限制环路

然而,较低的功率限制设置虽能降低 FET 上的应力,但会减少热插拔控制器需要限制的电流量,导致电流检测放大器可以检测的 VSNS 降低。VSNS 较低会产生较大误差,因为理论上,电流检测放大器的失调电压会限制可能功率限制的设置。方程式 1 为大多数热插拔控制器提供了建议检测电压(VSNS - MIN):

方程式 1

在高电流应用中,需要较高的电流限制阈值,因此必须设置更高的 PLIM,才能满足 VSNS - MIN 标准。PLIM 升高后,需要更高的 MOSFET SOA,这使得很难找到合适的 MOSFET 来实现大功率设计。例如,一个 12V、250A 的设计要求 FET 能够在 100°C 处理 560W 的功率应力,持续时间为 1ms,而现有的商用 FET 无法达到这一要求。

对于具有较大输出电容的设计,输出(dv/dt)控制电路可在启动期间处理 FET 功率应力。放置在栅极 - GND 之间的电容器 Cdv/dt 可限制栅极和输出电压的压摆率,从而限制浪涌电流。

图 2 展示了带有输出 dv/dt 控制的典型启动波形。为确保 MOSFET 保持在其 SOA 范围内,必须设置足够低的压摆率和适当的 Cdv/dt 值。当 MOSFET 中的功率损耗降低且分布在较长时间段内时,它们能够处理更多能量。因此,随着输出电容的增加,需要更高的 Cdv/dt 来降低 FET 在启动期间的浪涌电流和功率损耗。例如,要使特定 FET 在 SOA 范围内运行,10mF 的输出电容可能需要 47nF 的 Cdv/dt,而 30mF 的输出电容则需要 330nF 的 Cdv/dt。

图 2:带有输出 dv/dt 控制的启动

在启动至短路期间,热插拔控制器要求路径中流过一定量的电流(方程式 2 中的 IDS - INS),才能检测并触发功率限制故障。

方程式 2

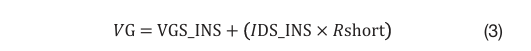

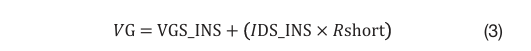

较大的 Cdv/dt 会减慢栅极电压斜升速率,导致延迟达到建立 IDS - INS 所需的栅极电压,从而增加故障检测时间,并使 MOSFET 承受很大的 SOA 应力。尤其是当短路阻抗(Rshort)升高时,这种影响更为明显,该阻抗由方程式 3 定义,如图 3 所示:

方程式 3

图 3:高阻抗短路下的栅极电路

考虑一个包含两种不同阻抗的输出短路情况:5mΩ 和 50mΩ。如果在启动期间发生 5mΩ 短路,随着栅极电压逐渐升高,短路电流会快速上升,短短 6ms 便会达到功率限制阈值(300W),达到阈值后将触发 TTIMER 并关断 FET。而 50mΩ 短路阻抗会减慢短路电流的上升速度,热插拔控制器需要大约 50ms 来检测 300W 的功率限制阈值,该瓦数对应 15J 能量,如此巨大的能量可能会损坏 FET,如图 5 所示。

图 4:5mΩ 阻抗短路时 FET 上的功率应力

图 5:50mΩ 阻抗短路时 FET 上的功率应力

为解决上述问题,混合热插拔解决方案应运而生。该方案包含一个与传统热插拔电路并联的电子保险丝,如图 6 所示。在这个电路中,电子保险丝利用其集成的过热保护功能来应对高应力事件。

电子保险丝的 PGOOD 信号连接到热插拔控制器的使能引脚,热插拔控制器的 PGOOD 信号则连接到下游负载的使能引脚。这些连接确保了以下几点:

- 热插拔 FET 仅在电子保险丝将大型输出电容器充电到接近输入电压后导通。此时 FET 启动时两端电压几乎为零,从而在启动期间消除功率应力。

- 下游负载仅在热插拔 FET 得到完全增强后启用,这样 FET 能提供低阻抗路径(与电子保险丝相比)并共享大部分负载电流。

- 电子保险丝在所有故障情况下均承受功率应力,而热插拔 FET 在任何情况下均不受应力影响。

图 7 说明了启动期间和不同故障情况下的电路功能。状态 1 至 5 描述了启动期间的事件顺序,状态 6 至 9 则是不同故障情况的中间状态。

图 7:混合热插拔解决方案流程图

混合热插拔方案的主要优势在于,热插拔 FET 的 SOA 不再是关键因素。开发者可以选择超低漏源导通电阻(RDS (ON))的 FET,这类 FET 通常价格更低,并且能大幅减少 FET 的数量。

在设计混合热插拔电路时,有几个关键要点需要注意。首先是热插拔路径中并联 FET 的数量。建议让 FET 在稳定状态下运行,使结温低于 100°C。可以通过方程式 4 计算给定负载电流下所需的并联 FET 数量:

方程式 4

其次是电子保险丝的选择。TPS1663 电子保险丝具有集成的热调节环路,可在大容性负载下实现零噪声启动。在稳定状态下,热插拔路径提供比电子保险丝路径更低的阻抗,因此能共享大部分负载电流。热插拔控制器决定过流保护阈值,应将此阈值设置为刚好超过负载电流。对于电子保险丝,将电流限制设置为其值(TPS1663 为 6A),以便在系统启动期间实现快的输出电容器充电速度。

另外,TTIMER 对 FET SOA 来说不再关键,因为在混合热插拔架构中,热插拔 FET 不受任何应力影响。可以仅根据负载瞬态要求选择故障计时器持续时间设置。

在大功率设计中,由于使用多个并联 FET,而热插拔控制器的栅极驱动强度有限,这会增加 FET 的开通延迟时间。因此,建议在开启下游负载时添加额外的延迟(5ms 范围内),以便为热插拔控制器提供足够的时间来完全增强 FET。

图 8 展示了一个使用 LM25066 热插拔控制器和 TPS1663 电子保险丝的示例混合热插拔电路,该电路具有 12V 输入、250A 负载电流和 30mF 输出电容。

图 8:混合热插拔电路

面向应力事件的混合热插拔解决方案使用 LM25066 评估板和用于 TPS26633 和 TPS16630 的评估模块,具有 30mF 输出电容器和 10A 热插拔电流限制,并且已经过验证。

图 9 显示了该电路的启动和稳定状态行为。在启动期间,为输出电容器充电所需的整个电流会流经电子保险丝,此时热插拔路径尚未启用。启动阶段过后,几乎整个负载电流都会流经热插拔路径,因为它是低阻抗路径。

图 9:在 30mF 电容下启动

图 10 显示了输出端短路的电路的启动行为。电子保险丝在启动时进入热调节模式,并在热调节超时后关闭;每隔 650ms 持续不断地定期重试,直到输出故障消除。由于热插拔 FET 保持关闭,因此 FET 上没有应力。

图 10:启动至短路

发生过载故障时,热插拔电路在关断 FET 前会产生过载电流,并持续计时器时间。图 11 显示了热插拔 FET 关断后,整个负载电流传输至电子保险丝路径,从而触发电流限制并终触发热关断。

图 11:过载故障期间的电路响应

图 12 显示了在稳定状态下发生输出短路故障时的电路行为。热插拔和电子保险丝都立即关闭,以保护输入电源免受损坏。电子保险丝会持续不断地定期重试,热插拔 FET 则保持关断,直到电子保险丝成功启动。

图 12:输出短路期间的电路响应