“buck

芯片 FB

引脚串联一个 1k 的

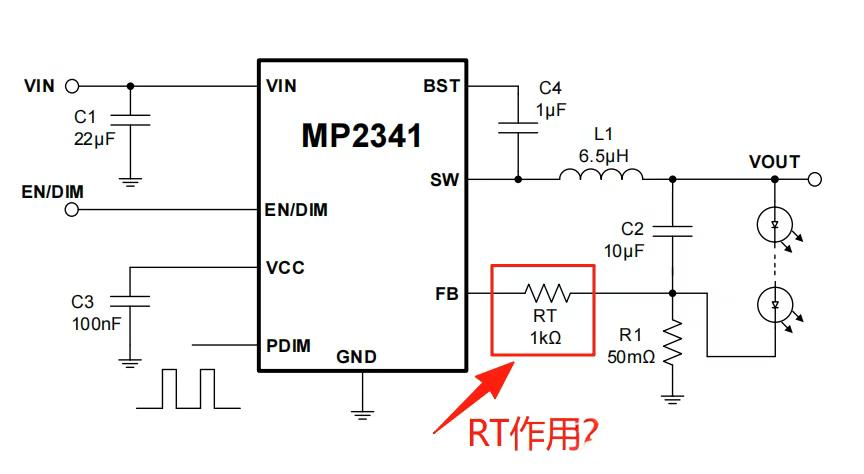

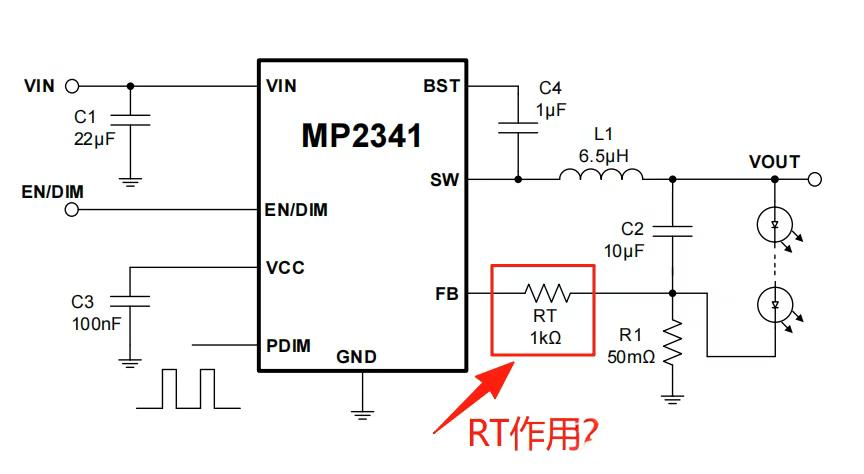

电阻是干什么的?” 前几天群里有小伙伴就提出了:“这颗芯片的 FB 引脚为什么串了一个 1kΩ 的电阻?”,并给出了如下图 1 所示的 RT 情况。

说实在的,buck 电路应用在

电子设计中是比较常见的,不过这种在 FB 引脚串联 1k 电阻的情况可能很多人也是次看到。带着这个问题,我们去查阅了这颗芯片的技术手册,期望从中找到答案。一般来说,应用中的问题大多可以在规格书中查到,所以对于硬件工程师而言,熟练掌握阅读各类规格书的能力是非常重要的。这不仅要求工程师能够总览全局,进行粗略的阅读,更要粗中有细,学会精读。

芯片的功能框图,通常硬件工程师在应用方面关注较多,而做芯片的工程师或者 AE 会对其进行更深入的研究。

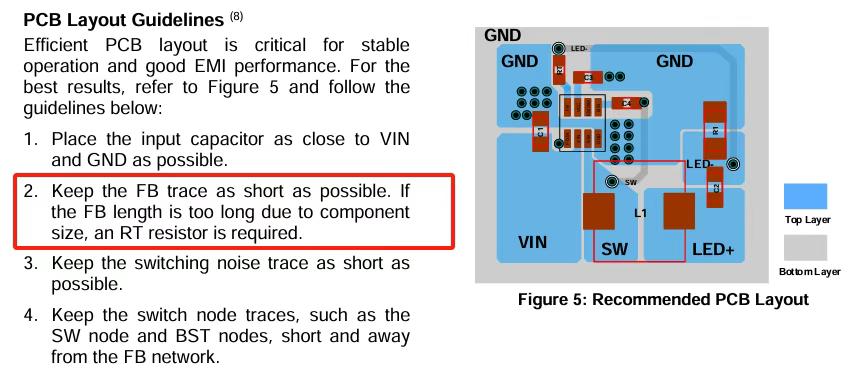

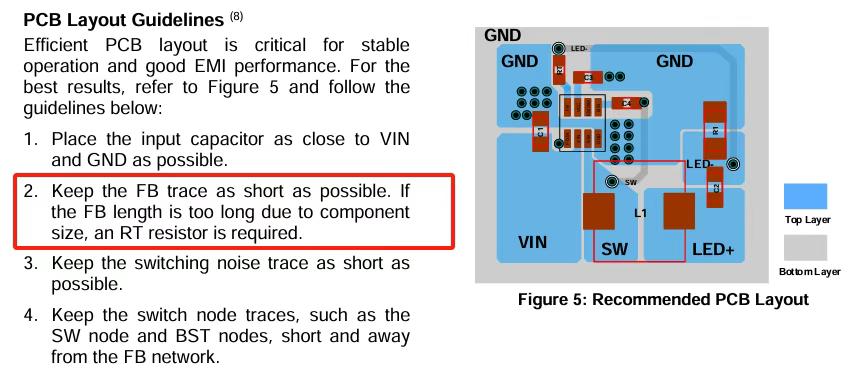

我们在 PCB Layout Guidelines 这里找到了答案。对于 FB 引脚,在走线时尽量保持越短越好。因为 FB 引脚反馈信号的准确性对于 buck 芯片的稳定工作至关重要,如果反馈线过长,可能会引入干扰和信号延迟等问题,影响芯片的性能。而当因为一些外围器件尺寸问题导致反馈线太长时,就需要加一个 RT 电阻。这个电阻可以起到一定的缓冲和调节作用,减少长走线带来的不利影响。

规格书上其实还有很多细节的东西值得我们去挖掘。比如每个引脚功能及应用注意点,在典型设计中,buck 电路中的各个器件如何选型,都有相应的计算公式。另外,还有芯片各种模式和场景下的测试图形,这些都有助于我们积累知识。许多工程师常常问如何提升自己的能力,其实多关注这些细节,日积月累就会有所提高。