在

电子电路设计中,不同电压电平之间的转换是一个常见且重要的问题。特别是在 3.3V 与 5V 电路之间的电平转换,对于许多电子设备的正常运行至关重要。本文将详细介绍使用 NMOS 管实现 3.3V 与 5V/12V 电路之间的电平转换方法,包括电路图设计注意事项、工作原理分析、实际测试结果以及探讨,尤其关注低温条件下 NMOS 体

二极管导通压降对信号的影响。

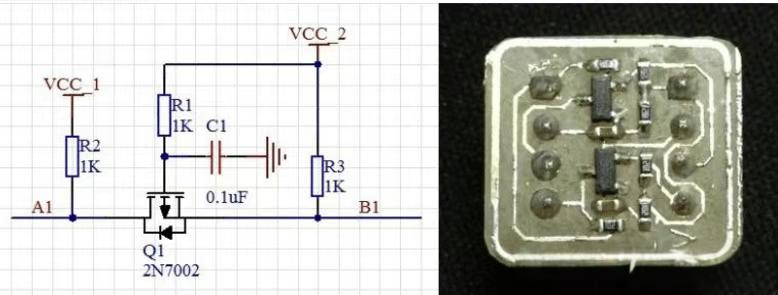

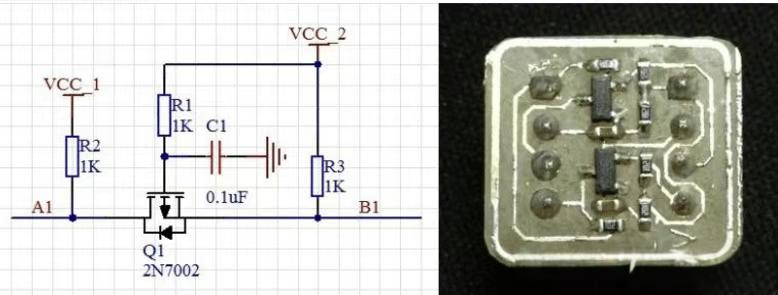

在设计使用 NMOS 管进行电平转换的电路时,需要特别注意 NMOS 管的连接方式。NMOS 管的 Source 端应接低电平侧,Drain 端接高电平侧,否则通过 NMOS 体二极管可能会存在漏电现象。

如图所示,SDA1/SCL1,SDA2/SCL2 为 I2C 的两个信号端,VDD1 和 VDD2 为这两个信号的高电平电压。该电路的应用限制条件如下:

- VDD1 ≤ VDD2;

- SDA1/SCL1 的低电平门限大于 0.7V 左右(视 NMOS 内的二极管压降而定),具体可参考本文分析章节;

- Vgs ≤ VDD1;

- Vds ≤ VDD2;

- 信号频率做不到很快。

对于 3.3V 和 5V/12V 等电路的相互转换,NMOS 管选择 AP2306 或者 SI2306 即可。

3.3V 部分的总线线路通过上拉电阻 Rp 上拉至 3.3V。此时,NMOS 管的栅极和源极都是 3.3V,所以它的 Vgs 低于阀值电压,NMOS 管不导通。这就允许 5V 部分的总线线路通过它的上拉电阻 Rp 上拉到 5V。此时两部分的总线线路都是高电平,只是电压电平不同。

当一个 3.3V 器件将总线线路下拉到低电平时,NMOS 管的源极也变成低电平,而栅极是 3.3V,Vgs 上升高于阀值,NMOS 管开始导通。然后 5V 部分的总线线路通过导通的 NMOS 管被 3.3V 器件下拉到低电平。此时,两部分的总线线路都是低电平,而且电压电平相同。

当一个 5V 的器件下拉总线线路到低电平时,NMOS 管的漏极基底二极管导通,源极电压为基底二极管导通 0.7V,3.3V 部分被下拉直到 Vgs 超过阀值,NMOS 管开始导通。3.3V 部分的总线线路通过导通的 NMOS 管被 5V 的器件进一步下拉到低电平。此时,两部分的总线线路都是低电平,而且电压电平相同。

- 适用于低频信号电平转换,价格低廉:该电路对于低频信号的电平转换效果较好,并且所使用的 NMOS 管价格相对较低,能够有效降低成本。

- 导通后,压降比三极管小:与三极管相比,NMOS 管导通后的压降更小,能够减少能量损耗。

- 正反向双向导通,相当于机械开关:NMOS 管具有正反向双向导通的特性,类似于机械开关,使用起来更加方便。

- 电压型驱动,当然也需要一定的驱动电流,而且有的应用也许比三极管大:虽然 NMOS 管是电压型驱动,但在某些应用中,所需的驱动电流可能比三极管大。

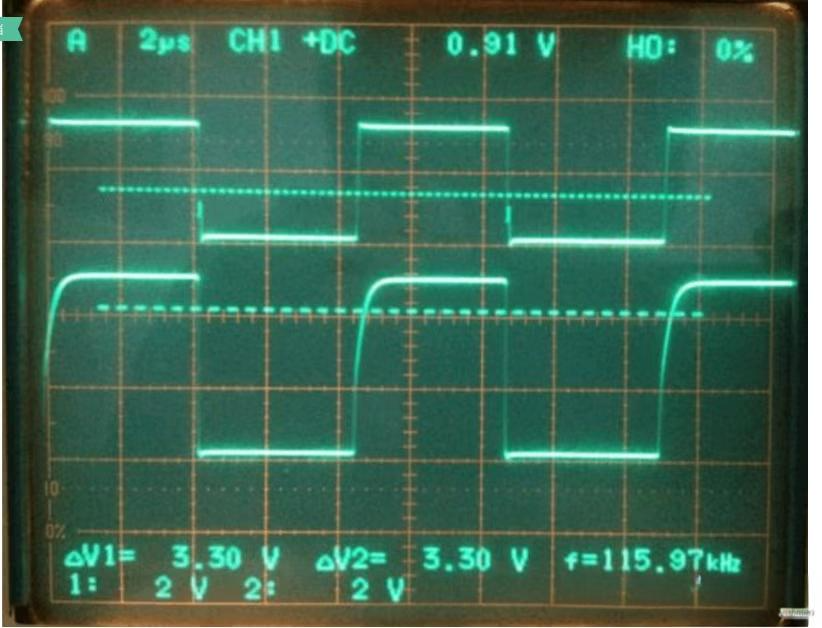

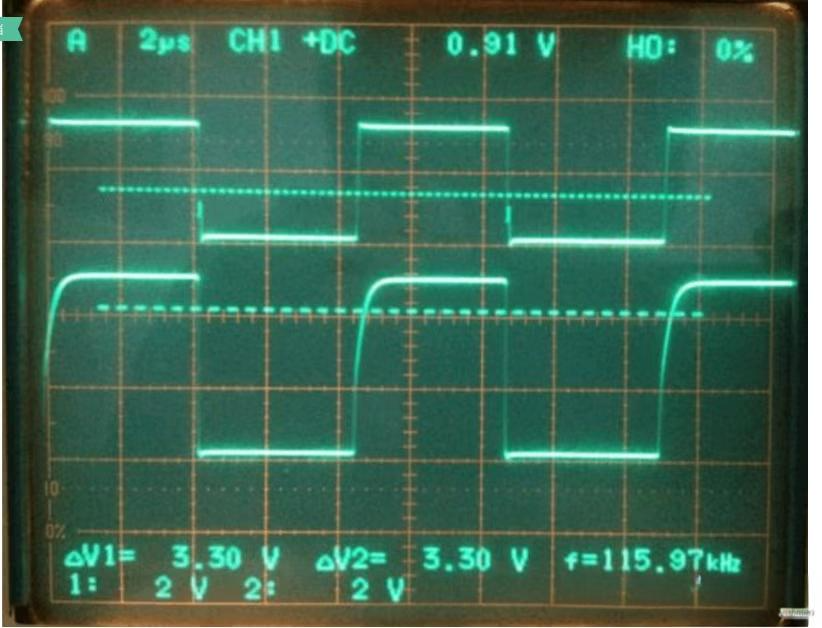

对这个电路进行测试时,MOS 管采用的是 2N7002 小信号 NMOS,其输入电容很小,大概几十 pF。

以下是不同频率下的测试波形:

- 115KHz 波形:这是常用串口较高的波特率。

分析可知,5V 电路上升沿缓是因为依靠上拉电阻上升至 5V,时间常数决定,上拉电阻越小上升时间越小;5V 电路下降沿陡是因为 NMOS 导通,直接由 3.3V 电路驱动低电平。 - 400KHz:高速 IIC 通信的时钟频率。

- 1MHz:波形上升太慢了。

- 4MHz:已经不能输出 5V 的电平了。

分析可得,5V 电路还没来得及上升至 5V 就被拉下来了。

- 问题描述:某颗以太网 PHY 芯片,MDIO 电压设定为 1.35V(1.5V - 10%),其对接的 MDIO 工具为 3.3V,利用 NMOS 进行电平转换。由于 NMOS 体二极管的导通压降的存在,导致 MDIO 工具输出 0 的时候,PHY 端的 MDIO 会有 0. 几伏的电压(体二极管导通压降)。参照 datasheet,当 PHY 芯片 MDIO 工作在 1.5V 时,Vil (1.5V) 只有 0.3V,导致不能正常工作。

- 为什么低温的时候才能复现:NMOS 管体二极管在低温下导通电压会变大。

由于 MOS 管的 Vth 和 Rds (on) 都受到温度的影响,因此温度也会间接影响 MOS 管的导通电压。具体来说,当温度升高时,Vth 降低而 Rds (on) 增大,这会导致 MOS 管在相同的 VGS 下更容易导通,但导通后的压降也会增大。然而,需要注意的是,MOS 管的导通电压并不是一个简单的固定值,而是受到多种因素(如 VGS、温度、沟道长度等)的共同影响。因此,在实际应用中,需要综合考虑这些因素来确定 MOS 管的导通电压。