在

电子电路设计领域,坏情况电路设计是确保电路在各种不利条件下仍能稳定工作的重要方法。而在进行坏情况电路设计时,元件容差是一个不可忽视的关键因素。下面我们将详细探讨元件容差的概念、在产品设计中的作用以及在不同电路中的计算和影响。

容差的概念在工业生产的各个领域,容差都是一个至关重要的概念。在电子行业中,容差指的是产品或零部件的参数(或质量特性值)的容许变化范围。从工程角度来看,由于生产过程中难以做到完全,所以需要规定指标允许有一定的变动量,这个变动量就是容差。它涵盖了机械加工中的几何参数以及物理、化学、电学等学科的参数。

例如,手表走时的误差、产品测试过程中的向量偏差、设备状态参数允许变化的范围以及棉纱单位面积的瑕疵点数等都属于容差的范畴。在机械制造中,容差通常被称为公差,包括尺寸公差、形状公差、位置公差等,其目的是使产品的几何参数变动量在一定范围内,以满足互换或配合的要求。从统计角度而言,某一指标的容许变化范围即为容差;从设计质量角度看,容差是一种允许极限,是从经济角度考虑允许质量特性值的波动范围,它贯穿于产品的整个寿命周期,是重要的技术信息。

容差在产品设计中扮演着举足轻重的角色。对于某一产品,如果容差设置过松,虽然生产成本可能较低,但产品的质量与可靠性、装配性能、维修性、保障性、测试性、安全性等方面可能难以达到设计要求;反之,若容差过紧,虽然质量能够得到保障,但制造过程需要更高的要求和成本。因此,容差在质量与成本之间起到了平衡的作用,它不仅影响产品的质量与可靠性、功能实现、工艺方法选择,还对产品的生产制造成本、使用维护成本及全寿命周期成本产生显著影响。

在当今竞争激烈的市场环境下,制造企业面临着诸多挑战,如缩短生产时间、提高性能质量、降低制造成本、提供优质服务以及保持清洁环境等。而容差设计的课题就是解决质量与成本之间的平衡问题。然而,目前考虑无源元件容差的参考文献相对较少,且大多是从科学家的角度而非电路设计师的角度出发。不过,通过利用基本的电路公式和元件极限值来计算某个电路参数在设备生命周期内坏情况下的取值范围,我们可以更好地理解坏情况的设计。

电阻器作为电子电路的基本元件,其容差计算需要详细考虑。电阻器规定有购买容差 P,常见的容差实例有 0.5%、1%、2%、5% 和 10%,购买容差保证电阻器在购买时其阻值在标称值之内。但在装配过程中,如焊接等外部应力会使电阻器阻值改变,在完工的装配件出厂之前,电阻器阻值变化可能会超过购买容差。此外,温度、老化、压力、湿度、装配、阳光和灰尘等外部应力会导致元件值在其生命周期内不断变化,这种变化称为漂移容差 D,也以百分比来度量。

电阻器的制造工艺和工作环境决定了漂移容差。制造商通常采用稳定而可控的方法和抗漂移材料来制作容差严格的电阻器,但在现场环境中,漂移仍难以完全避免。一般来说,在 - 25℃~+85℃的环境温度及合理外应力作用下,温度漂移是不可预测的,电阻器阻值可能会因温度升高而增大或减小。在采用较低漂移容差之前,设计师应向电阻器制造商咨询。

计算终的电阻器阻值时,可使用 (1±T) R1 来得到坏情况的电阻器阻值,其中 T 是用小数表示的总容差。例如,对于 R1=10 kΩ、容差为 5% 的电阻器,其坏情况的值为 (1 + 0.01 (5) + 0.01 (5)) R1 = 1.1R1 = 11 kΩ,值为 (1 - 0.01P - 0.01D) R1 = (1 - 0.05 - 0.05) R1 = 9 kΩ。对于

电容器容差的计算,可采用相同的方法,但由于各制造商制作电容器的方法差异较大,各类电容器之间的容差差别也比电阻器大得多,一般建议将所有电容器容差增大至三倍,除非制造商另有说明。

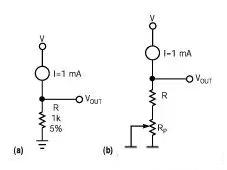

在非比例计量电路中,必须取的电阻器容差,因为两种容差不会相消。例如,利用公式 VOUT = IR 计算输出电压时,若 I 是一个理想的 1mA 电流源,R 是一个容差为 5% 的电阻器,则 VOUT = 1mA (1 ± 0.05 ± 0.05) 1 kΩ = (1 ± 0.05 ± 0.05) V,其范围为 0.9V ≤ VOUT ≤ 1.1V。为了缩小 VOUT 的范围,可以增加另一只电阻器来调节初始容差。

可变电阻器阻值 RP 的计算步骤如下:

- 选择小于计算值 R = 0.9 kΩ 的接近的十进阻值 R,该值为 R = 0.82 kΩ;

- 计算所选电阻器的阻值:RMIN = (1 - P - D) R = 0.9 (0.82) = 0.738 kΩ;

- 可变电阻器 RP 必须补偿 RMIN 和 1kΩ 之差,所以 RPMIN = 1 - 0.738 = 0.262 kΩ;

- 考虑电位器的容差,RP = RPMIN / (1 - T) = 0.262 kΩ / (1 - D - P) = 0.262 / 0.8 = 0.328 kΩ;

- 选择 RP = 500Ω。

终得到的阻值为:R = 820Ω,RP = 500Ω。但有些工程师认为,坏情况的设计程序可能过于严格,使用的电位器阻值较大,分辨率较低,电位器漂移误差较大。解决这一问题的方法可以是冒险降低电位器阻值,或者使用精度更高的部件。非比例电路必须考虑容差的偏移,一个 5% 的购买容差会导致 20% (±10%) 的总容差。

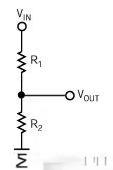

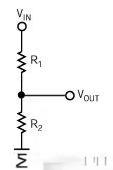

分压器是典型的比例计量电路,其容差的某些部分在公式中会相消。为了得到增益值,需要将 R2 的容差设定得大,而把 R1 的容差设定得小。当分压器中两只电阻器的容差同时很大或很小时,两种容差就会相消。如果电阻器制造商保证在环境温度变化时所有电阻器以相同方向按比例漂移,则温度容差也会相消。与非比例电路相比,比例电路只取容差 T,而非两倍容差 2T。

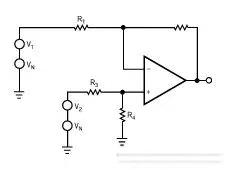

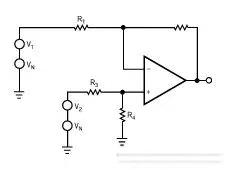

许多参考文献指出,用分立元件制作一个具有良好共模抑制(CMR)的精密差分放大器是比较困难的。通过对差分放大器的容差分析可以发现,电阻器容差和

运算放大器误差会将 CMR 限制在大约 100 dB 以下。当总容差为 1%(对 0.5% 电阻器来说,为 P + D)时,电阻器容差可以导致 CMR 的范围从高达运算放大器极限值到低至 - 34.89dB。考虑到 1% 电阻器的购买容差和漂移容差,总的 CMR 可能低至 - 24.17 dB。在没有共模电压而有差分输入信号的情况下,这一误差就变成增益误差。

由于采用分立元件的差分放大器难以制作和微调,大多数设计师会使用具有内置微调电阻器的 IC 差分放大器,廉价的 IC 差分放大器具有高达 - 86dB 的 CMR。