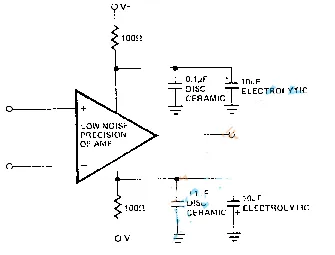

电源去耦:典型的串联稳压器供电的电源中包含幅度为 150μV、频率范围为 100Hz - 100KHz 的噪声,开关型电源的噪声情况更为严重。运放的 PSRR 在高频时以 20dB/Decade 的速度降低,通过在电源脚加 RC 或 LC 去耦网络,能滤除大部分噪声,电路形式如图 3 所示。不过在使用 RC 去耦时,需要注意负载电流的变化会导致对电源脚上电压的调制。

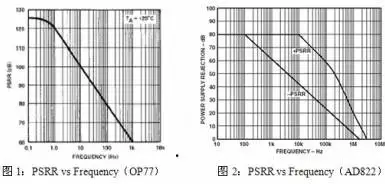

电源去耦:典型的串联稳压器供电的电源中包含幅度为 150μV、频率范围为 100Hz - 100KHz 的噪声,开关型电源的噪声情况更为严重。运放的 PSRR 在高频时以 20dB/Decade 的速度降低,通过在电源脚加 RC 或 LC 去耦网络,能滤除大部分噪声,电路形式如图 3 所示。不过在使用 RC 去耦时,需要注意负载电流的变化会导致对电源脚上电压的调制。 电源调整率:任何电源电压的变化都会引起运放输入偏置电流的变化。从图 1 可知,OP77 的 PSRR 在 DC 时是 126dB(0.5μV/V),电源电压的变化是一个潜在的低频噪声源。在低噪声运放的应用中,降低电源的纹波和提高电源的调整率都十分重要,电源调整率不足通常会引起讨厌的低频噪声。

电源调整率:任何电源电压的变化都会引起运放输入偏置电流的变化。从图 1 可知,OP77 的 PSRR 在 DC 时是 126dB(0.5μV/V),电源电压的变化是一个潜在的低频噪声源。在低噪声运放的应用中,降低电源的纹波和提高电源的调整率都十分重要,电源调整率不足通常会引起讨厌的低频噪声。 影响途径和对策

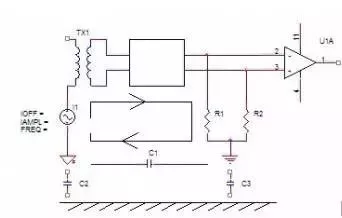

影响途径和对策 共模电流干扰:开关管漏极开关电压驱动的位移电流,通过初次级分布电容、次级电路、次级对大地与杂散电容、大地与初级地之间的杂散电容形成环路,次级模拟电路中流过的共模电流流过不平衡的阻抗转换成差模,对放大电路造成干扰(如图 6)。共模方式引入的干扰一般为开关噪声中的高频分量(数 MHz 以上)。对此的措施主要有提供一条从开关电源次级地返回初级地的低阻抗噪声旁路通道,通常使用 1000p - 2200p 的安规电容;使用共模扼流圈加强开关电源的输出的共模滤波;使用隔离技术,化回路中的共模电流。

共模电流干扰:开关管漏极开关电压驱动的位移电流,通过初次级分布电容、次级电路、次级对大地与杂散电容、大地与初级地之间的杂散电容形成环路,次级模拟电路中流过的共模电流流过不平衡的阻抗转换成差模,对放大电路造成干扰(如图 6)。共模方式引入的干扰一般为开关噪声中的高频分量(数 MHz 以上)。对此的措施主要有提供一条从开关电源次级地返回初级地的低阻抗噪声旁路通道,通常使用 1000p - 2200p 的安规电容;使用共模扼流圈加强开关电源的输出的共模滤波;使用隔离技术,化回路中的共模电流。 空间耦合干扰:噪声会通过空间磁场耦合到具有一定环路面积的信号回路或地线环中,造成对信号的影响。另外来自开关电源或市电网络的高频干扰可能通过空间杂散电容直接耦合到信号回路。在设计中,要合理布局、调整电感线圈或变压器放置方向、优化布线,减小关键信号的回路面积,避免形成地环路;双面或单面板布线时,注意信号线和地线、电源线与地线一定要贴近平行走线,使用 1000p 电容射频多点接地,兼顾 EMC 和低频信噪比的需求;对敏感电路加屏蔽,注意屏蔽层连接到被保护信号的参考地;走线设计上注意电源线不要和信号线捆扎在一起。

空间耦合干扰:噪声会通过空间磁场耦合到具有一定环路面积的信号回路或地线环中,造成对信号的影响。另外来自开关电源或市电网络的高频干扰可能通过空间杂散电容直接耦合到信号回路。在设计中,要合理布局、调整电感线圈或变压器放置方向、优化布线,减小关键信号的回路面积,避免形成地环路;双面或单面板布线时,注意信号线和地线、电源线与地线一定要贴近平行走线,使用 1000p 电容射频多点接地,兼顾 EMC 和低频信噪比的需求;对敏感电路加屏蔽,注意屏蔽层连接到被保护信号的参考地;走线设计上注意电源线不要和信号线捆扎在一起。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。