提高造率

快速动力学(宽带宽度和高振动率)和电流回馈

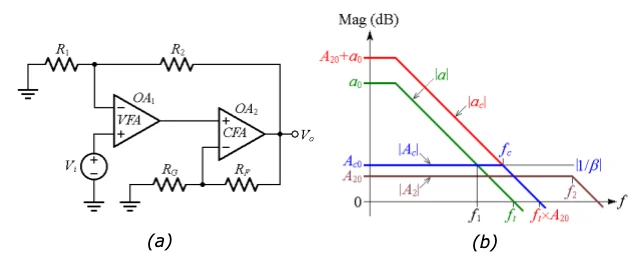

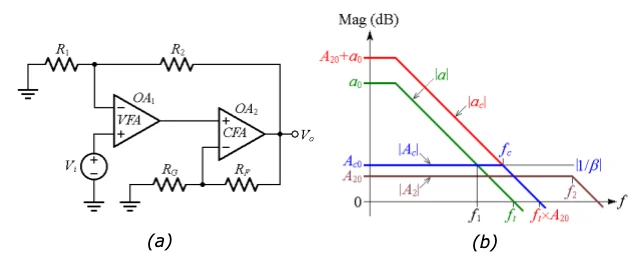

放大器(CFAS)的低稳定特性 使它们适合于高速应用。 另一方面,电压反馈放大器(VFAS)提供了更好的直流特性(低输入偏移电压和偏置电流,低热漂移),低噪声和高环的增益,因此它们更适合应用。图1(a)显示了结合两者的复合放大器。

使用电流回馈放大器和bode图的复合放大器电路,用于更高的振荡速率图1。 (a)使用电流回馈放大器(CFA)实现更高的振荡速率的复合放大器。 (b)直线bode图,同时,图1(b)显示了直线bode图:

| A |是VFA的开环增益,而F t是其过渡频率(当前演绎中的F T = GBP)| A C |是复合放大器的开环增益

| A 2 |是CFA的闭环增益,F 2是其–3-DB频率| A C |是复合放大器的闭环增益,而F C是–3-DB频率|β|是复合放大器周围的反馈因素

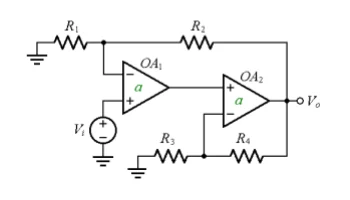

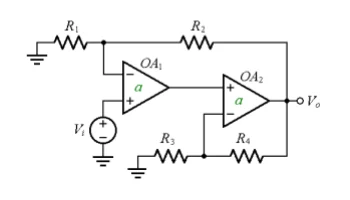

A 0,A C0和20识别上述收益的DC值 该电路类似于上一篇文章的图1(a)的电路,如下所示。

复合放大器可实现更宽的带宽

但是,我们的新电路的精神截然不同。

OA 2不再是与OA 1相同类型的

运算放大器,而是一个更快的设备,其极频率F 2的设计被设计为超过 OA 1的F T,因此它不会侵蚀复合放大器的相位边缘。如图1(b)所示,OA 2 上移的存在是整个开环增益| A | OA 1的创建复合开环增益| A C |。

给定| 1/β|的值如手头的应用所决定的那样,我们如何指定20相对于| 1/β|的值?答案是强加\ [a_ {20} \ leq \ left | \ frac {1} {\ beta} \ right | \]

(当然,我们不能制作20 > | 1/β|,因为这将使交叉频率f c在f t上方,其中| a c |的较

高频线将破坏电路的稳定。 为了获得更好的见解,请考虑图2的PSP

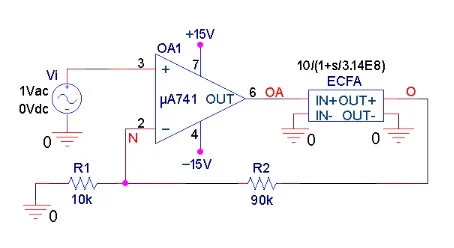

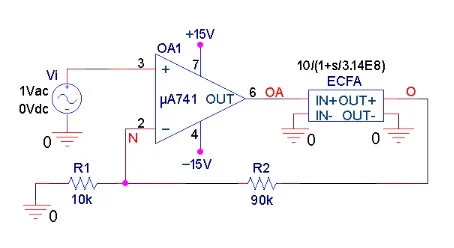

ICE电路,模拟741 Op-Amp,并使用Laplace块模拟为20 = 10 = 10 V/V(= 20 dB)和F 2 = 50 MHz配置的CFA。在此示例中,我们使用“ =”符号应用了上述方程式。

图2。一个复合放大器,以提高741运算放大器的SR。

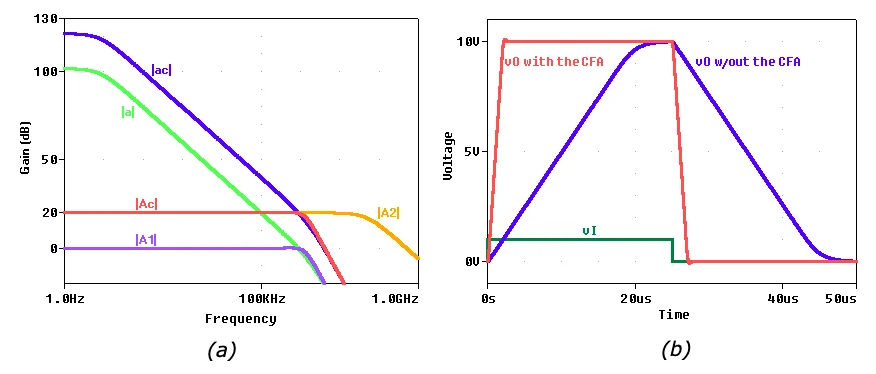

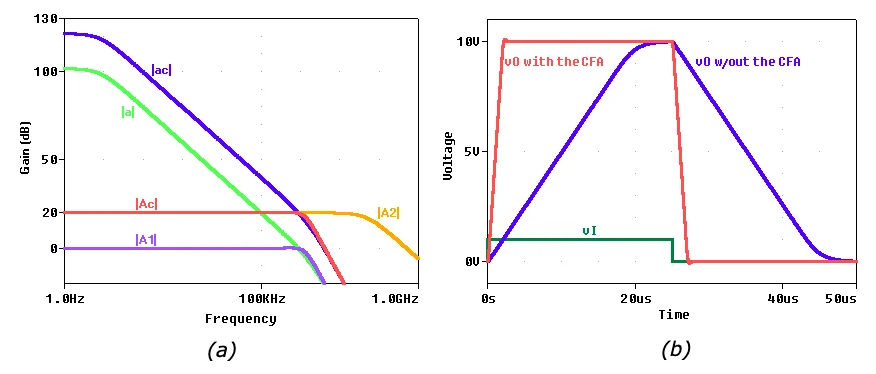

参考图3(a),我们发现OA 1必须仅扩大0 dB,而通过10 v/v进行扩增,CFA由CFA进行。OA 1较小的输出电压波动应大大改善驱动率(SR)。 频域和时域的PSPICE电路图

图3。 图2的PSPICE电路的图显示了(a)频域和(b)时域中的情况。

果然,通过将图2的输入源更改为脉冲类型获得的图3(b)的时间响应证实了我们的期望。在没有CFA的情况下,根据数据表,SR = 10/20 = 0.5 v/μs,741将大约20μs挥动,因此根据数据表。使用CFA,复合放大器的SR是更快的数量级或约5 v/μs的顺序。

我们还注意到,在DC环路增益和复合放大器的–3-DB频率带宽中,缩放顺序增加。

让我们回想一下上一篇文章中的等式1 :

\ [f_b = \ frac {gbp} {a} \]

根据该公式,增益为10 v/v将暗示–3-DB的频率为100 kHz,而实际测量值为1.4 MHz。这要归功于CFA提供的帮助。

,我们指出,CFA输出阶段的任何过热将永远无法达到VFA的输入阶段,从而大大降低了输入热漂移的影响。