电子系统超小型化的一个关键挑战是电源管理。任何电气工程师都知道,当整个系统尺寸缩小时,可用于能量存储和能量转换的面积也会随之缩小。这种情况正在许多市场增长的应用中发生,例如植入式医疗设备、物联网电子产品和可穿戴电子产品。虽然电子产品的尺寸不断扩大,但存储能量所需的电池和

电容器却跟不上。结果是,能量存储和电源管理所需的面积常常主导终产品的整体外形尺寸。

由于这些面积限制,能量必须以有效的形式存储。通常,有效的形式具有更高的潜力并且具有显着的噪声成分。然后需要使用稳压器(例如 LDO)将该电源电压调节至系统运行的水平。

低功耗 LDO 设计的一个关键品质因数是电流效率。电流效率定义为 I负载 与 I总之比。该比率是从电源汲取并传递给负载的总功率的百分比。对于高功率应用,该数字通常超过 99%。然而,这在低功耗设计中是非常不同的。例如,如果总负载电流为 10uA,则 LDO 中每增加 1uA 静态电流就会导致电流效率下降 10%。在功率已经受限的系统中,这种效率损失可能是灾难性的。因此,限度降低总体 LDO 静态电流的设计方法至关重要。正确设计的 LDO 将保持整体系统效率和较长的电池寿命,从而限度地减少对大型储能元件的需求。

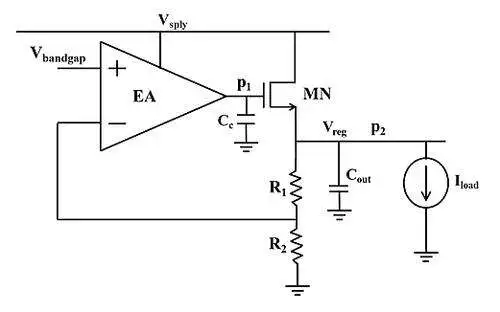

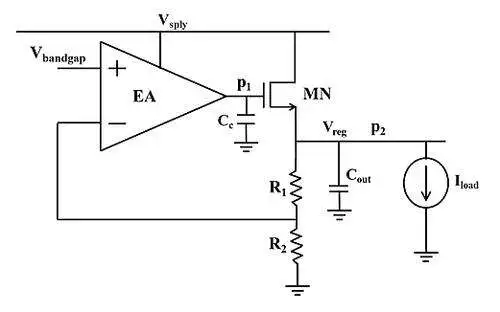

LDO 设计简短概述 图 1 显示了采用 NMOS 传输

晶体管的 LDO 框图。考虑未稳压电源电压 (V sply ) 远大于稳压输出电压 (V reg ) 的应用。在这里,简单的 NMOS 传输晶体管架构通常是选择。

图1

该架构具有许多理想的特性,其中两个是微不足道的频率补偿和较小的 FET 面积。 FET 面积较小是因为 NMOS FET(电子)中的电荷载流子迁移率高于 PMOS FET(空穴)。频率补偿之所以容易进行是因为主极点位于 NMOS 传输晶体管的栅极而不是输出节点。

LDO 通常是两极点系统,某些架构包括零极点和/或额外的高频极点。图 1 所示的 NMOS LDO 是一个简单的两极系统。因此,通过将极点 P1 的频率设置为比极点 P2 低十倍以上,可以实现稳定性。只要 P1 和 P2 这两个极点很好地分离,该 LDO 就会保持闭环稳定。这是假设误差

放大器是一个简单的 OTA,在输出节点有一个主极点。一旦确定了输出电容器大小 (C out )(由高频负载瞬态要求设置,例如数字逻辑

开关),即可计算极点 P1。 P1 由误差放大器输出阻抗 (r o ) 和补偿电容器 (C c )的乘积设置。通过增加 r o, 我们能够同时实现低 P1 频率和高环路增益,这都是非常理想的特性。

重要的是要记住,在 OTA 设计中,高输出阻抗不会消耗额外的电流,而只会消耗额外的面积。这使得 OTA 以及相应的 LDO 静态电流成为单位增益带宽所需的值。这是一项特定于应用的要求,为传统 LDO 架构中的静态电流设定了基线。在许多应用中,只需 100nA 至 200nA 的静态电流就足够了。这导致电流效率大于 98%。值得注意的是,转换速率增强型 LDO 能够低于该电流,但在尺寸和复杂性方面成本高昂。

因此,在 NMOS LDO 中,稳定性和低静态电流是齐头并进的。但没有什么是的。 NMOS LDO 有一个很大的缺点。电源电压(或开销电压)为 V gs(MN) + V sat(MN) + V reg ,约等于 2V sat(MN) + V th + V reg。即使使用本机阈值 NMOS 晶体管 (V th = ~0V),这也是使用 PMOS 传输晶体管的开销电压的两倍。这是阻碍 NMOS LDO 在许多应用中使用的主要缺点。还值得注意的是,通常不建议使用本机阈值 NMOS 传输晶体管。这是因为跨工艺角这些器件很难完全关闭,导致 V reg 漂移。