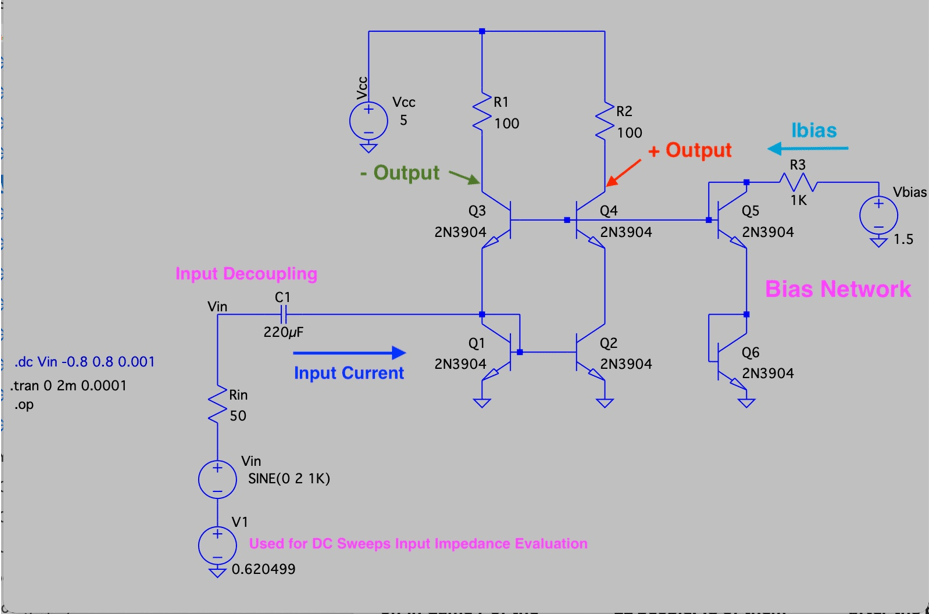

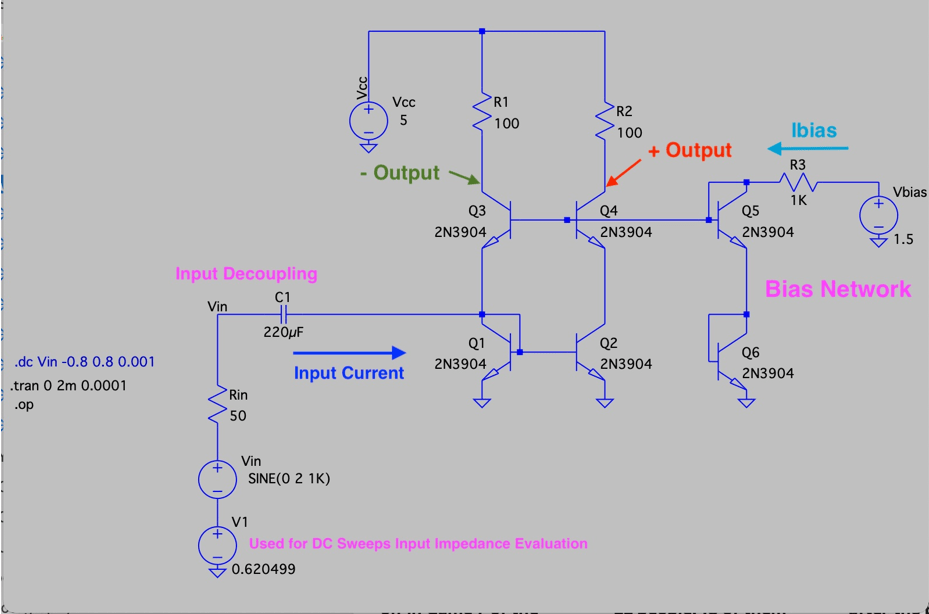

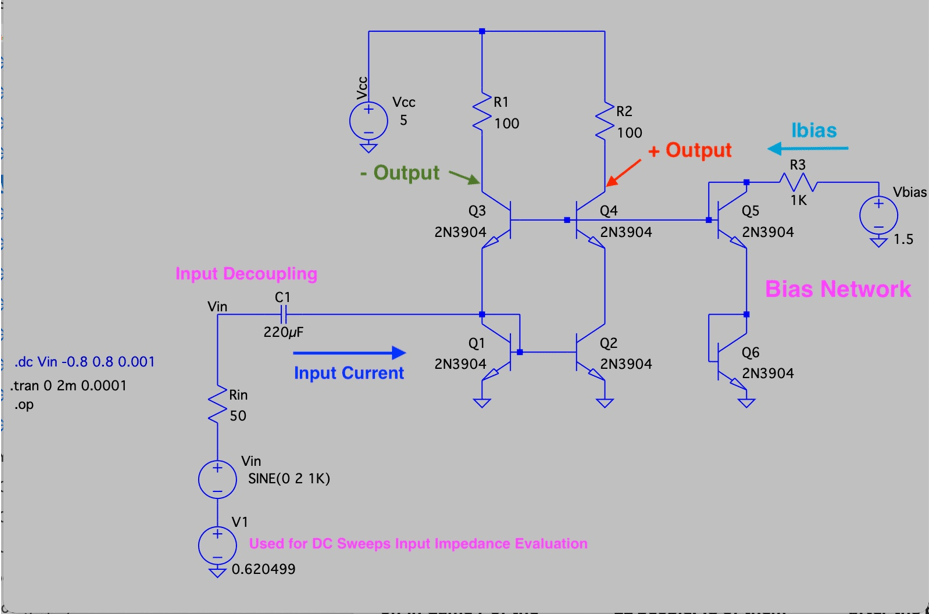

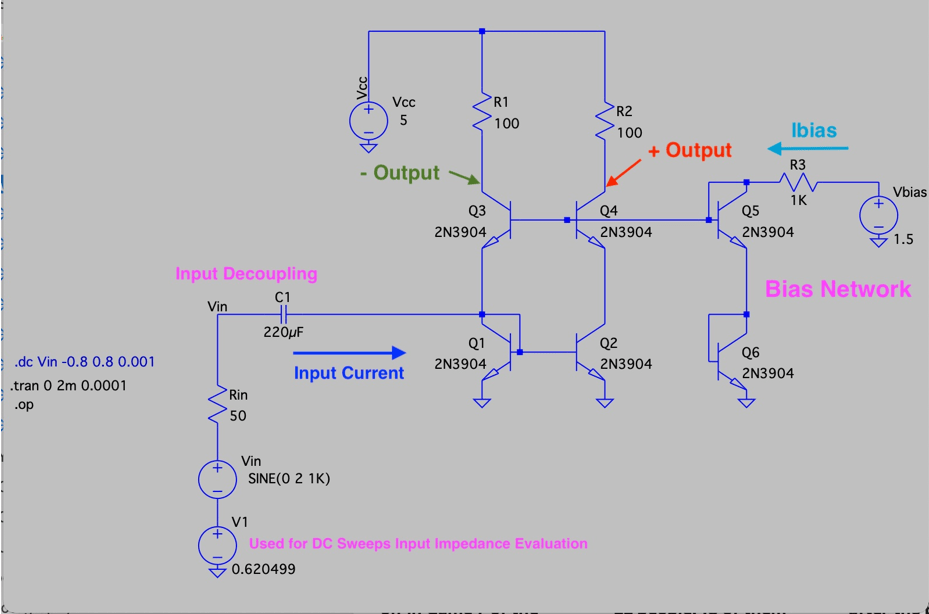

如图 1所示,采用 LTspice 实现,该电路采用独特配置的 6 个双极晶体管 (BJT),根据输入极性“引导”来自 Q3 和 Q4 的输出电流。

图 1微混频器拓扑的 LTspice 原理图,其中 6 个 BJT 的排列使得 Q3 和 Q4 的输出电流取决于输入极性。

它是如何运作的

C1 用作去耦

电容器,允许 Q1 基极的电位随 Q1

二极管连接的偏置 Vbe 变化。对于正输入信号,Q2 充当 Q1 的镜像,对于大的负输入信号则截止;而 Q3 在小信号条件下是共源共栅,并提供大的负输入电流。

对于理想的相同尺寸的晶体管,所有集电极电流都相等,并由 Q5 加 Q6 的基极-发射极电压设置,该电压由流过 R3 的电流(即 Ibias)确定。

当输入信号较大且为正时,输入电流主要流过 Q1,Q1 充当跨导器和共源共栅器件,而 Q3 随着其发射极电压上升而截止。 Q2 通过共源共栅器件 Q4“镜像”Q1 集电极电流,该器件将大正输入电流的副本吸收为正输出。

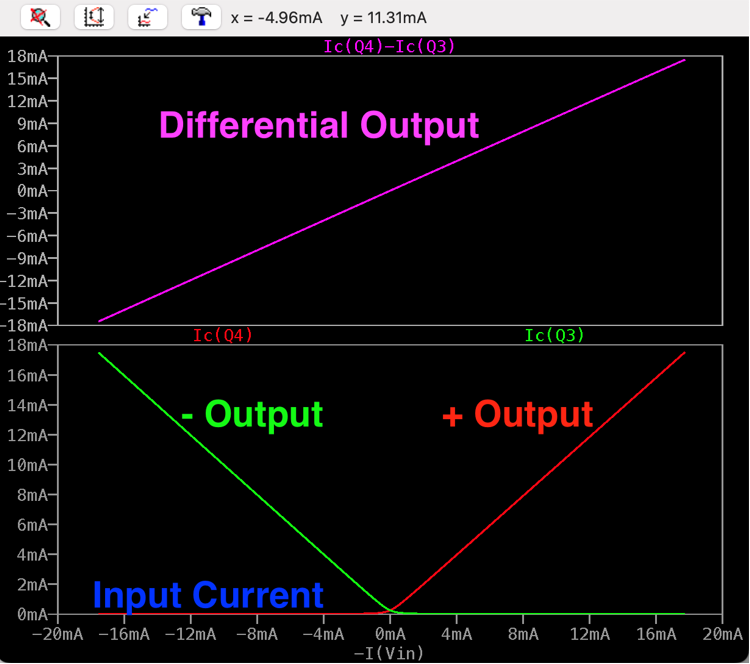

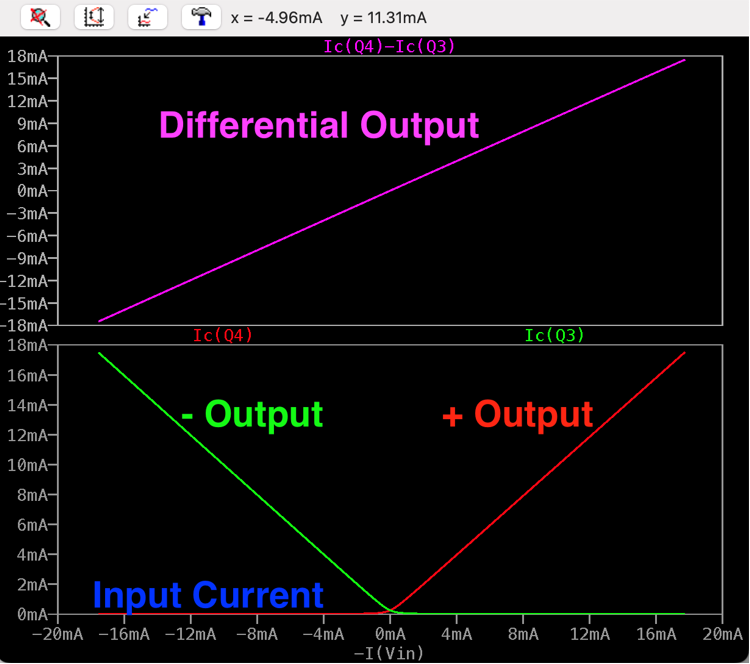

大信号输入 在大负输入上,所有输入电流均由 Q3 提供,因为其发射极电压下降且 Q1 截止,而 Q3 的集电极吸收负输出(图 2)。请注意,对于大的正输入,输出电流“定向”到 Q4 (+) 或 Q3(-),并且对于理想器件而言是无限的。

图 2响应大负信号输入的差分输出的 LTspice 仿真。

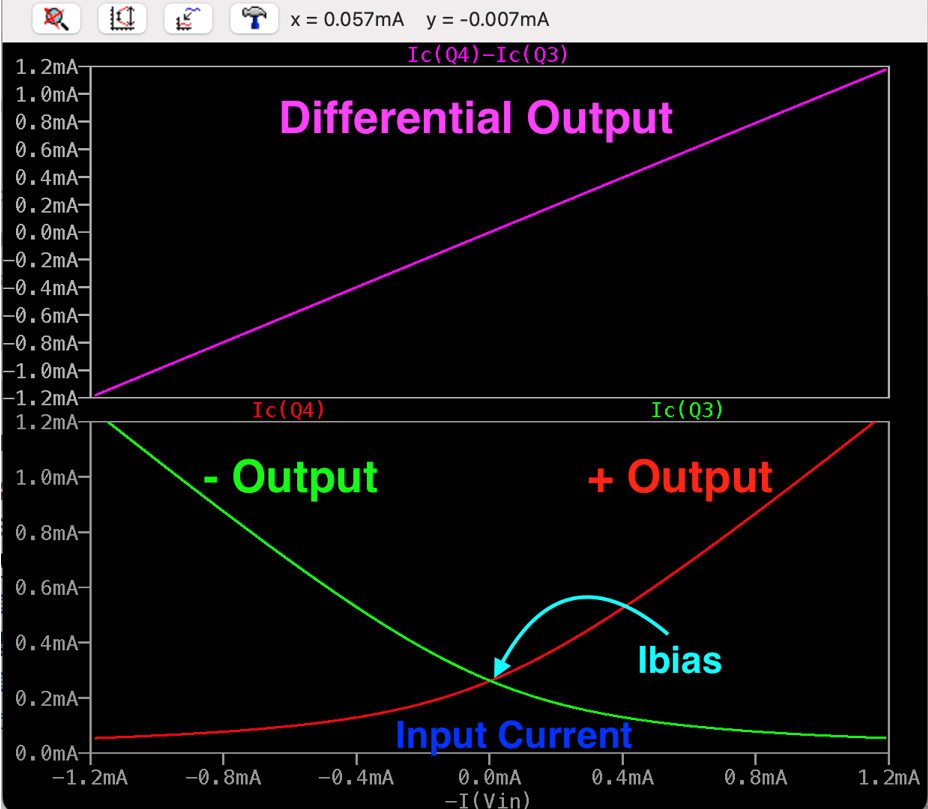

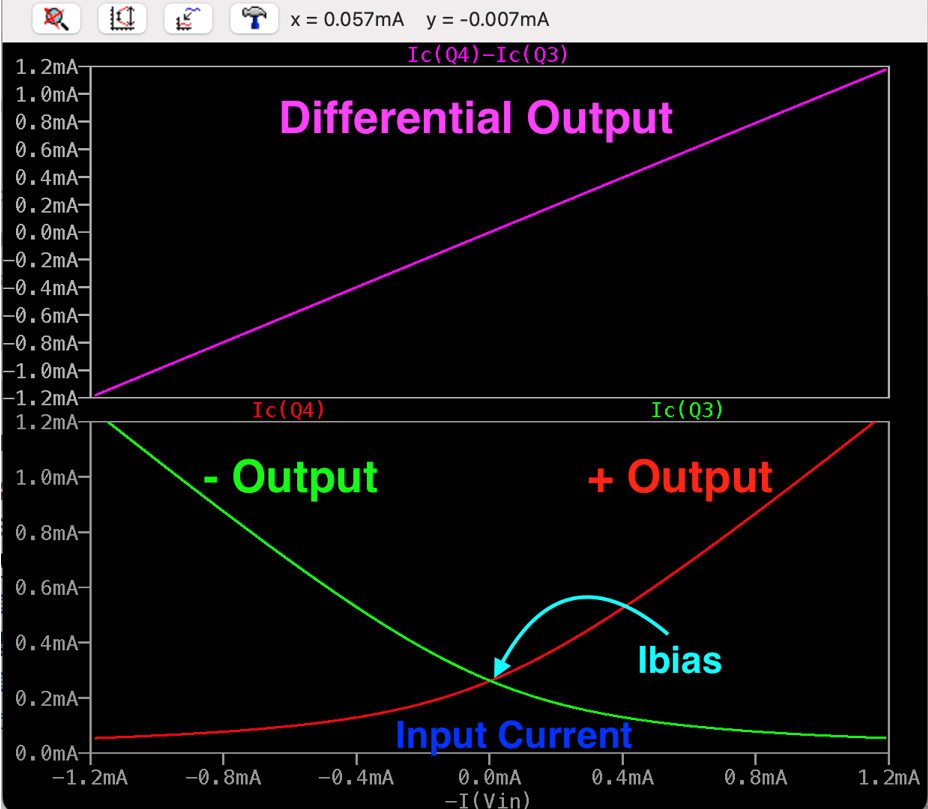

小信号输入 如图 3所示,输入较小时,电路的工作方式类似于小信号 A 类类型,因为所有晶体管都以 Ibias 集电极电流工作。因此,在输入电流为零的情况下,Q1 和 Q3 都传导 Ibias,Q2 和 Q4 也是如此,并且电路以差分输出工作。

图 3响应小负输入电流的差分输出的 LTspice 仿真。 实际结果

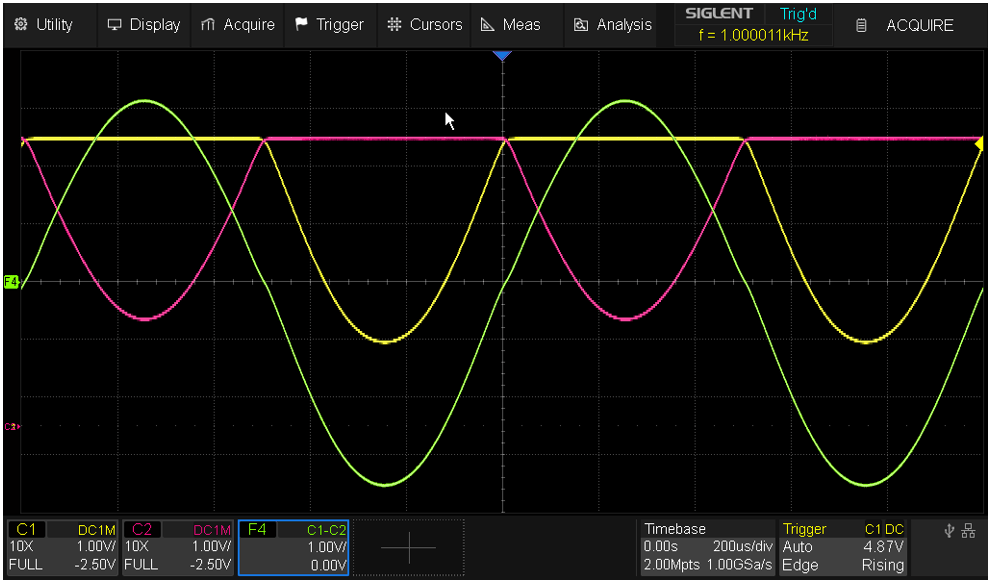

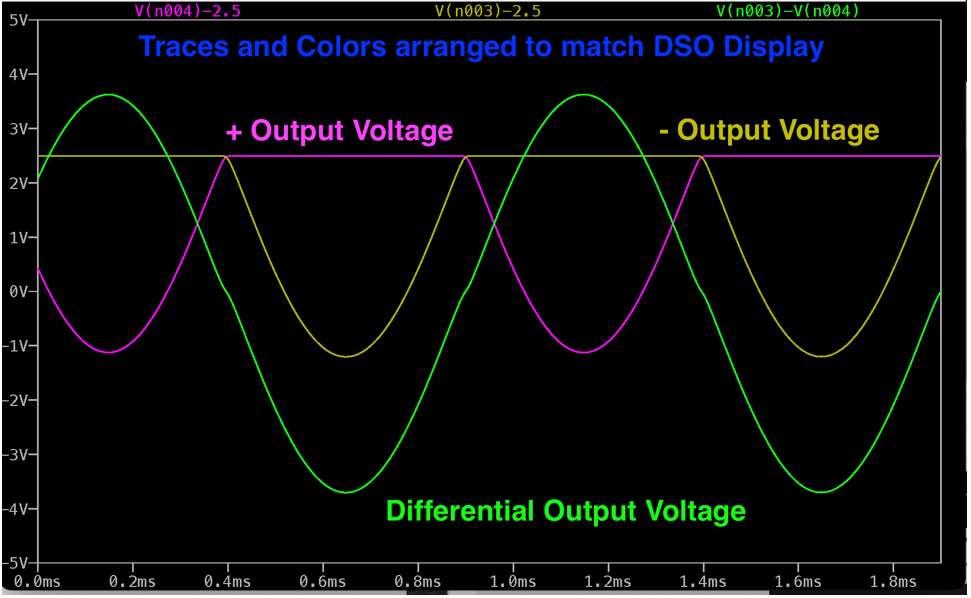

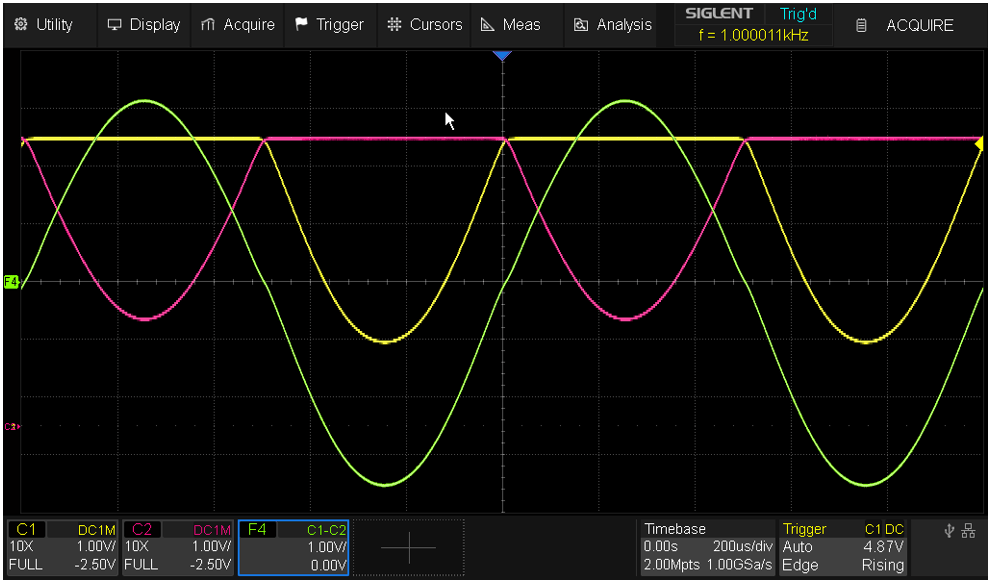

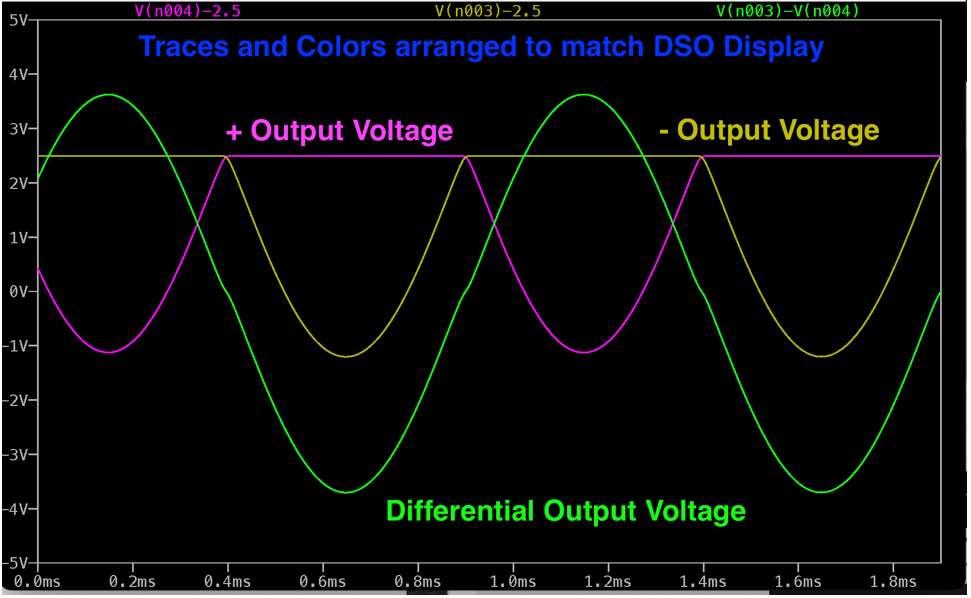

图 4显示了图 1 中电路的实际结果,显示在具有 2Vpp @ 1KHz 正弦波输入的 DSO 上。图 5显示了图 1 的 LTspice 模拟结果。请注意,LTspice 图是使用颜色和显示偏移偏差设置的,以匹配 DSO 显示以进行比较。 图 4 图1 原理图的实际结果显示在具有 2Vpp @ 1KHz 正弦波输入的 DSO 上。

图 5图 1 的 LTspice 模拟结果,其中使用颜色和显示偏移偏差设置绘图以匹配 DSO 显示以进行比较

另请注意 DSO 和 LTspice 结果中显示的轻微“交叉失真”,这对于传统 A/B 级来说很常见。这可以通过更高的 Ibias 来改善,但代价是

放大器功耗更高。

该拓扑结构提供了除单差分转换之外的附加功能 [1]。它将动态输入阻抗视为瞬时输入信号电平的函数;传统放大器讨论中经常未涉及的领域。

信号引起的失真始于有效放大器输入阻抗随动态信号电平变化并对抗源阻抗,创建非线性信号相关电压/功率分配器来调制输入信号电平。

改善输入阻抗 图 6显示了添加额外电阻以改善输入阻抗随输入信号电平变化的版本[2]。请注意,添加了额外的

电阻器,以帮助平衡大输入信号摆幅时的输入阻抗变化,同时仍然保持每个器件的集电极电流偏置相等(由 Ibias 确定)。

图 6具有附加电阻的高动态范围放大器,可帮助平衡大输入信号摆幅期间的输入阻抗变化,同时仍保持每个器件的集电极电流偏置相等(由 Ibias 确定)。

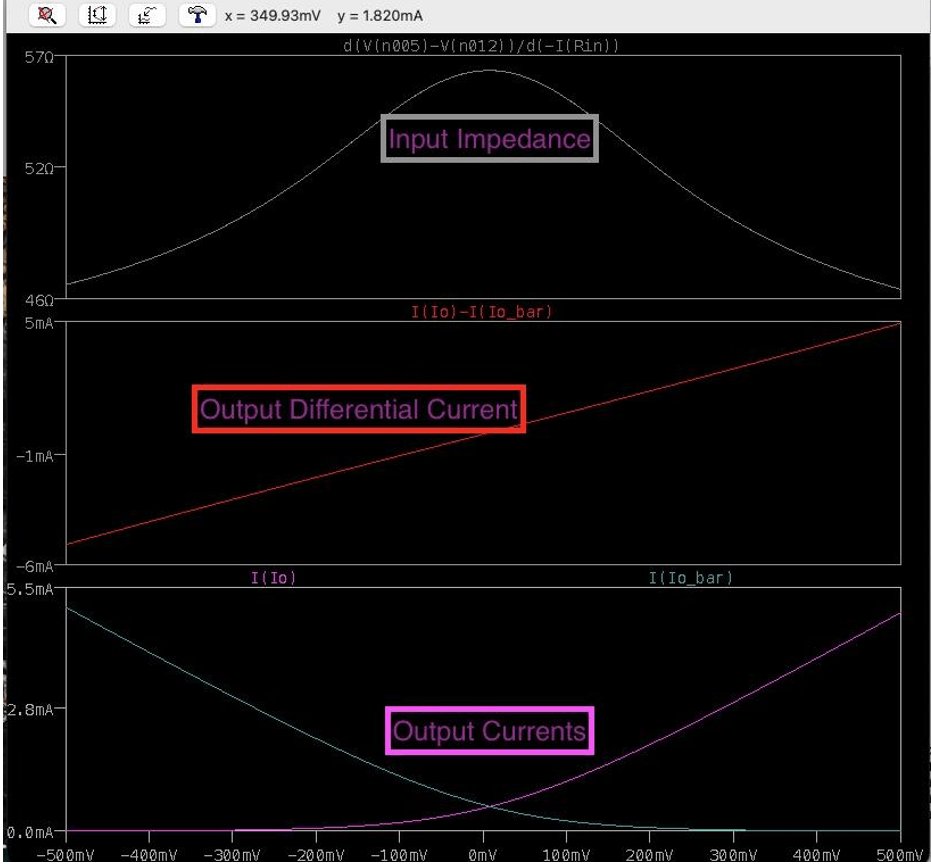

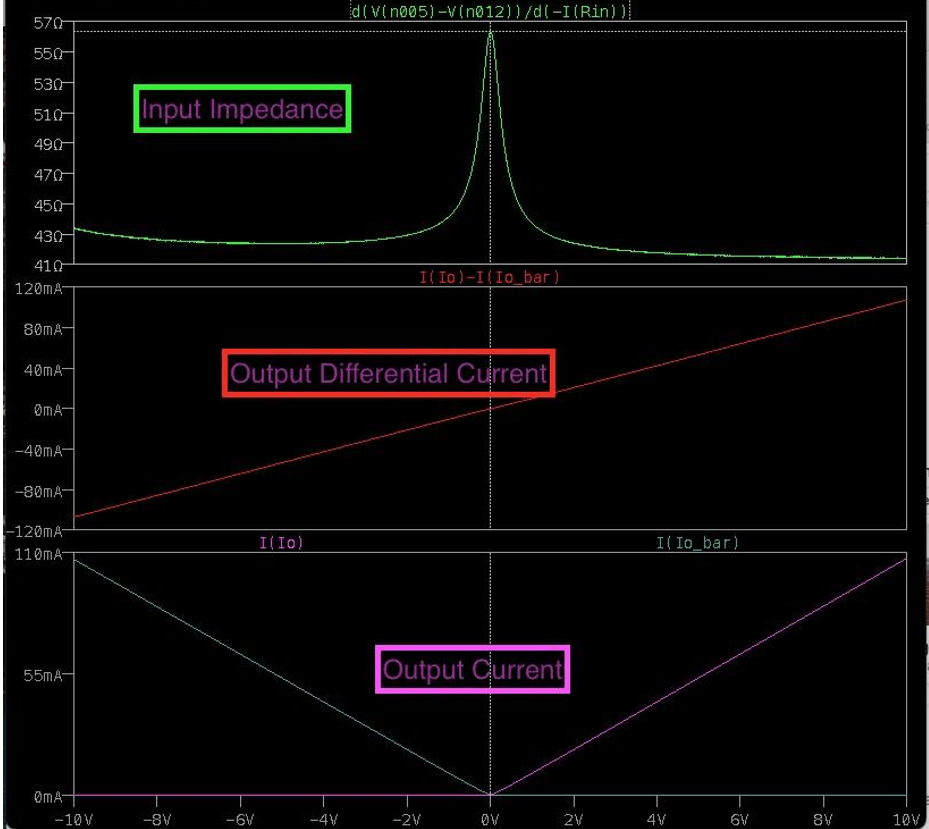

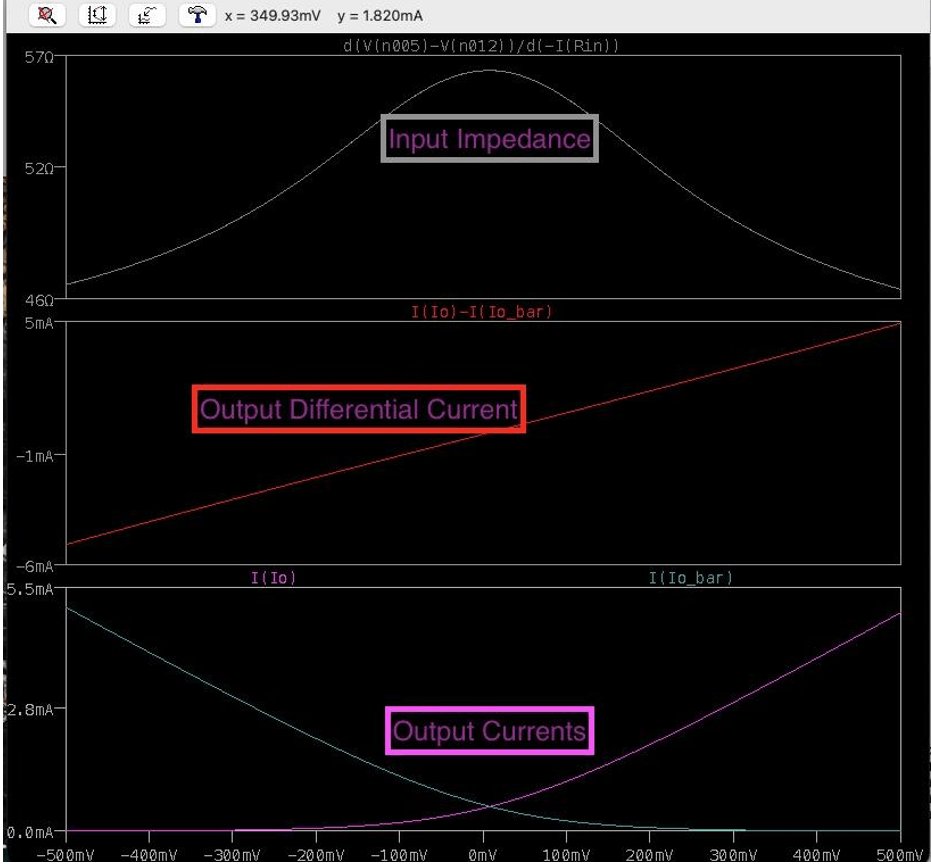

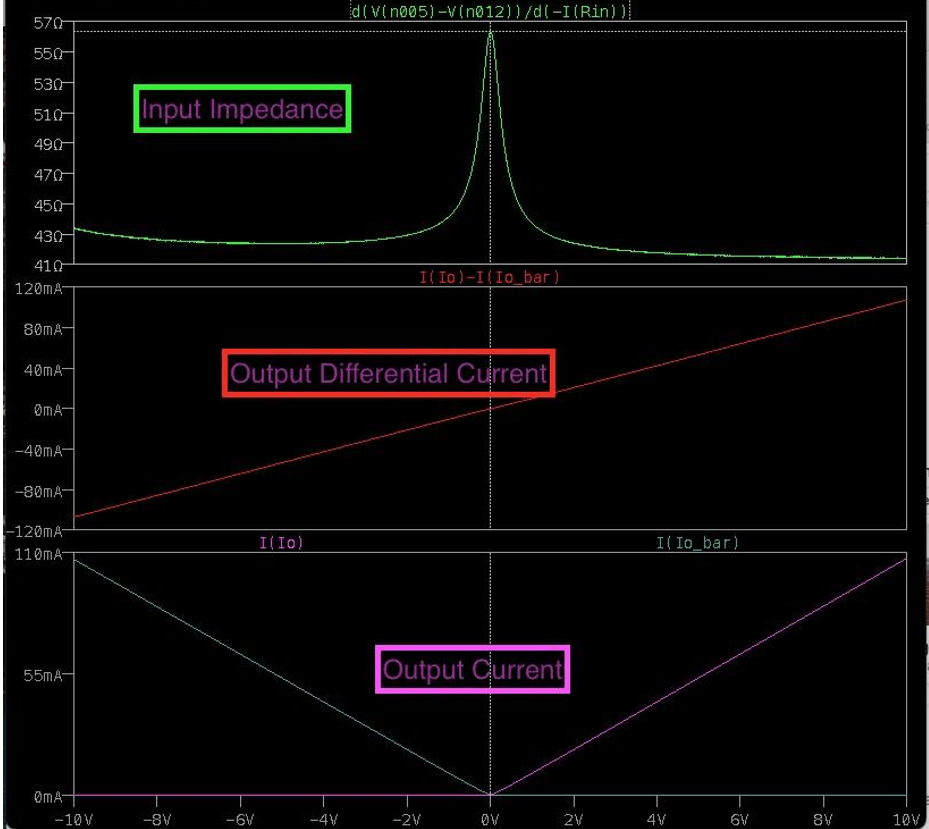

如图7和图 8所示,LTspice 输入阻抗结果是通过在输入扫过较大的正负范围时获取输入电压相对于输入电流的导数得出的。

图 7小信号输入阻抗结果和输出差分电流。

图 8大信号+ 10 V 峰值输入阻抗结果和输出差分电流。