逻辑门是数字电路,可对一个或多个输入信号执行逻辑运算以产生单个输出。每种类型的 logic gate 都根据真值表执行特定功能。以下是主要 logic gates 的简要说明:

AND:仅当所有输入都为高电平时,才会产生高输出

OR:如果至少有一个输入为高电平,则产生高输出

NOT:反转输入的状态,产生相反的输出

NAND:仅当所有输入都为高电平时,才会产生低输出

NOR:如果至少有一个输入为高电平,则产生低输出

XOR:如果输入不同,则产生高输出

XNOR:如果输入相等,则产生高输出

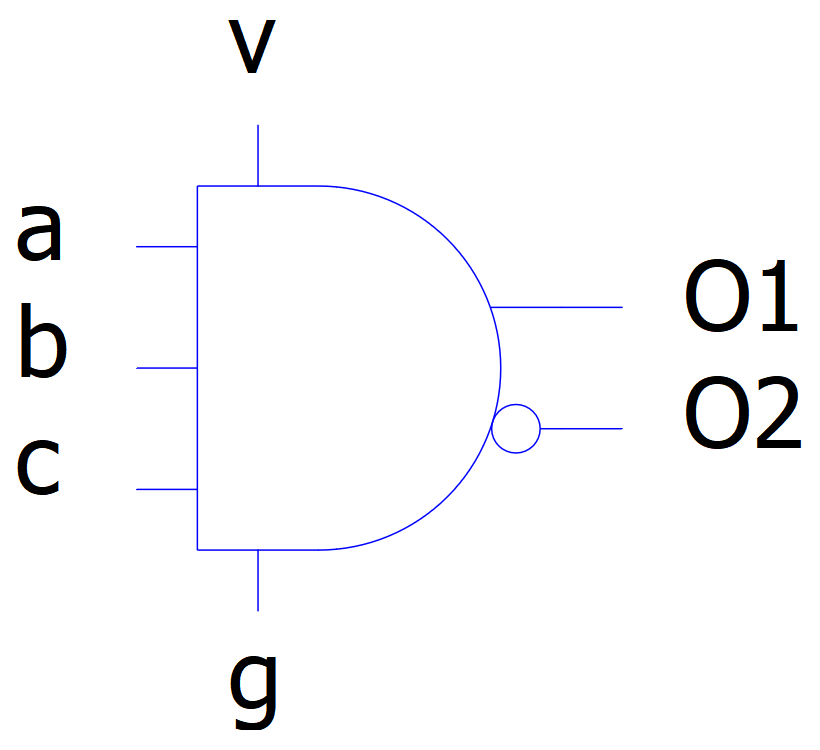

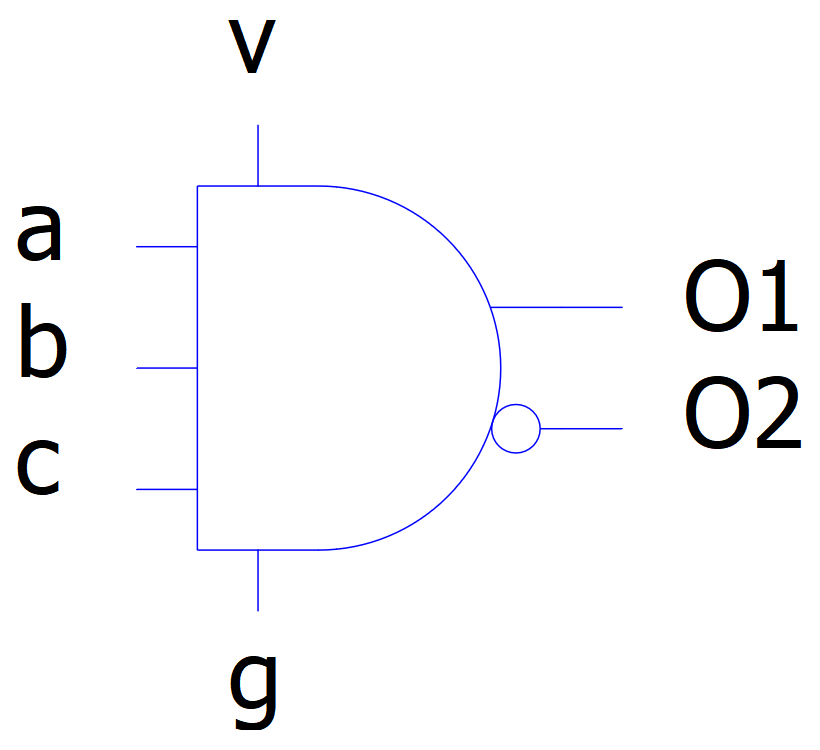

QSPICE 逻辑门必须通电才能正常工作,就像在实际

逻辑电路中一样。通常,QSPICE logic gate 具有以下引脚,如图 1 所示:

A:门的个输入

B:门的第二个输入

C:门的第三个输入

V:用于为栅极供电的引脚

G:接地引脚

O1:门的正常输出

O2:栅极的负(反)输出 对于每个门,QSPICE 提供标准模型、具有否定输出的模型以及具有两个输出的模型。设计人员可以选择适合仿真的模型,以及必要的输入数量(2、3、4、5)。将 logic gate 插入电路图后,将其引脚连接到电路的其他部分并开始仿真。

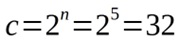

5 输入 AND 逻辑门的仿真

使用 QSPICE,可以构建包含逻辑门的电路图,并模拟它们在不同条件下的操作。以下示例执行 5 输入 AND 逻辑门的仿真。根据以下公式,这五种 logic state 以所有可能的组合进行处理,从而产生 32 种不同的配置:

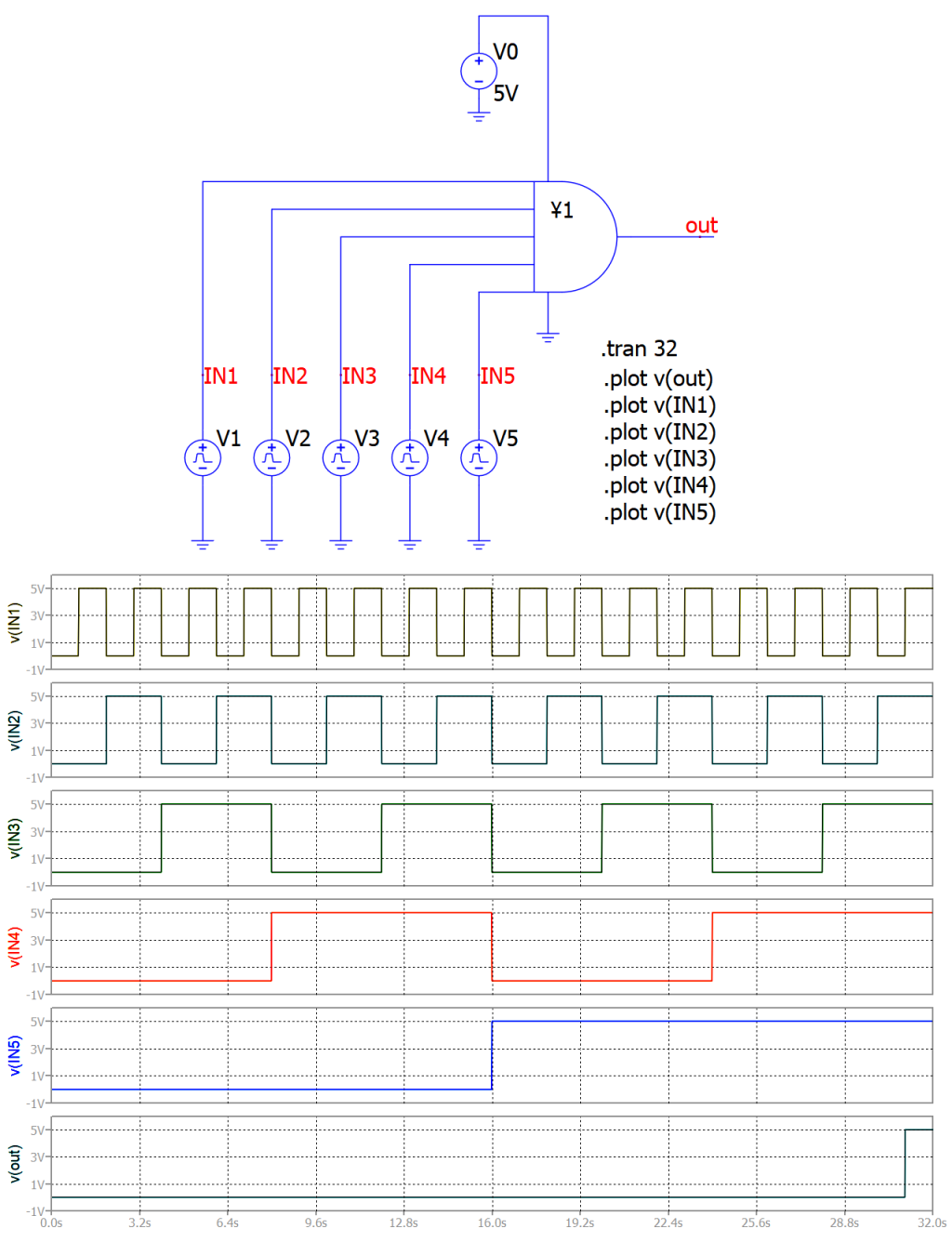

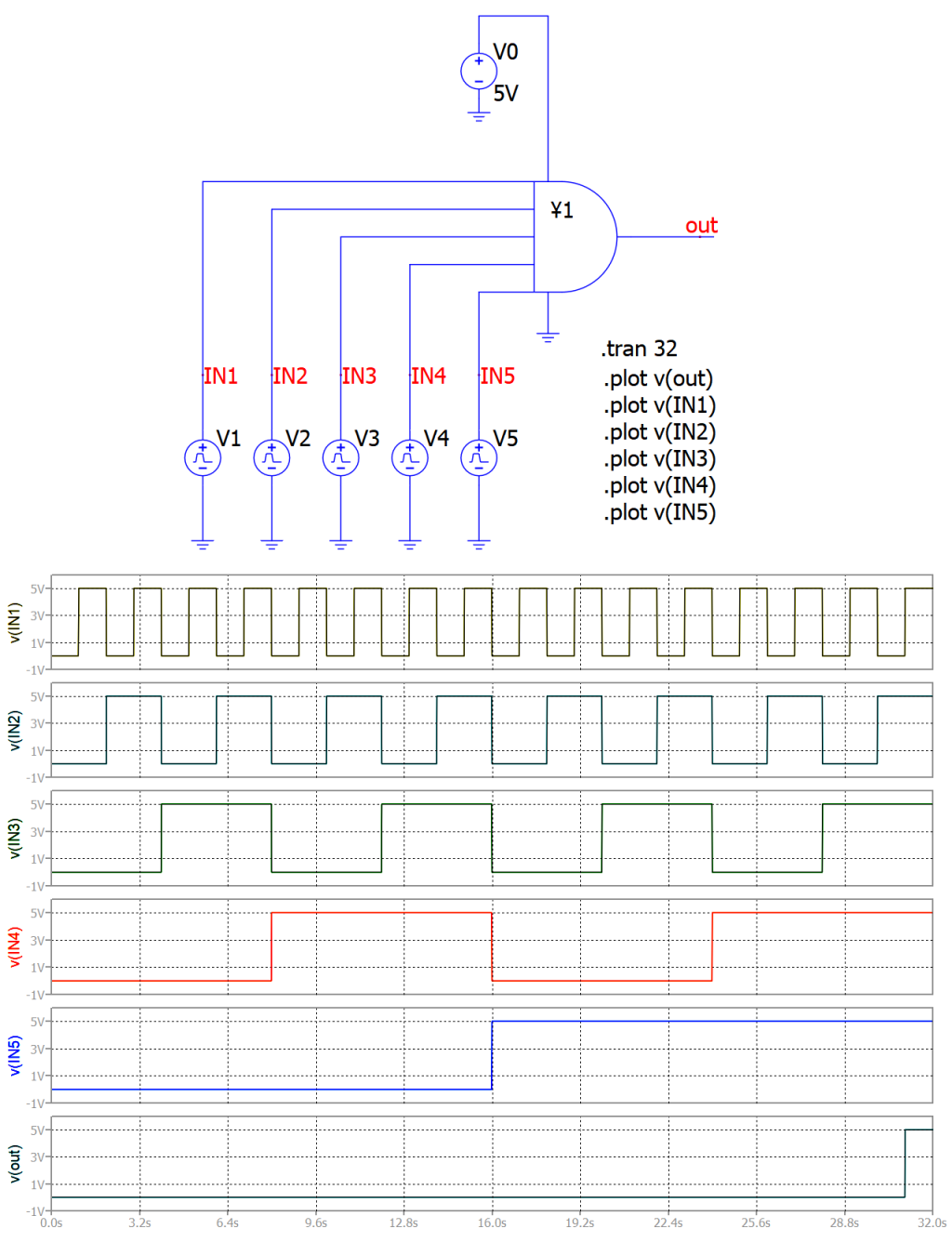

因此,我们创建一个新项目(参见图 2 中的电路图),并从“Behavioral”和“Gates”组中添加逻辑门“5-Input AND 门”。定位逻辑门后,需要定义电路的输入和输出以及电源

触点。输入可以连接到代表逻辑信号(0 和 1)的方波电压源。逻辑门的输出可以连接到负载电阻器,可以在负载电阻器上测量电压。五个信号发生器产生电位为 0 V (L) 和 5 V (H) 的方波。分析刚刚创建的系统的逻辑操作,我们可以查看输入和输出信号的波形,从而验证逻辑操作的正确性。如图所示,生成所有可能的信号组合,然后将其输入到逻辑门的相应输入中。

图 2:在 AND 逻辑门中,只有当所有输入都具有高逻辑值时,输出才会假定高逻辑值

使用真值表,可以立即读取两个或多个命题的结果,从而促进逻辑值的计算。如果 inputs 的数量增加,则与 output 的 logic state 相关的终组合的数量也会增加。在这种类型的 logic gate 中,根据下面的真值表,只有当所有 inputs 都具有高 logic value时,output 才假定高 logic value。

QSPICE:逻辑门(第 14 部分)

当然,您可以测试 circuit diagram 中 logic gate 的其他配置和 inputs的数量。请记住,无论解决方案建模如何,始终只有一个输出。

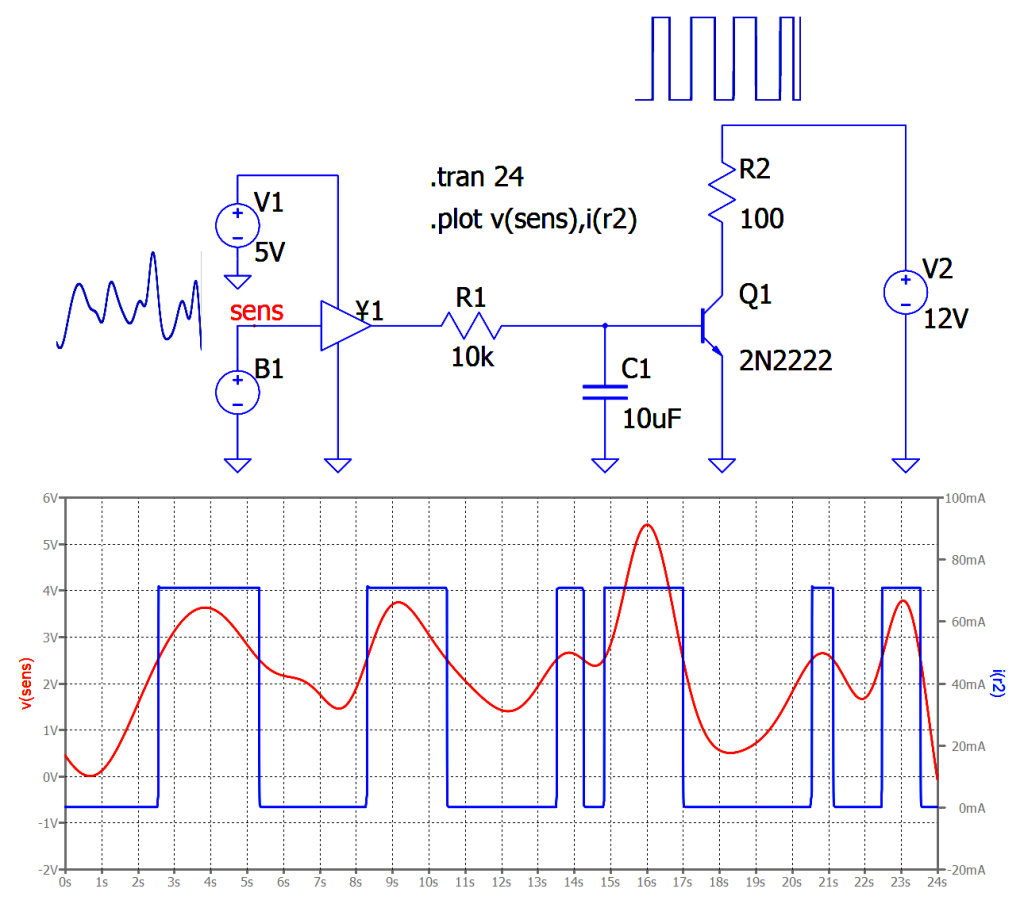

在特定温度下启动风扇

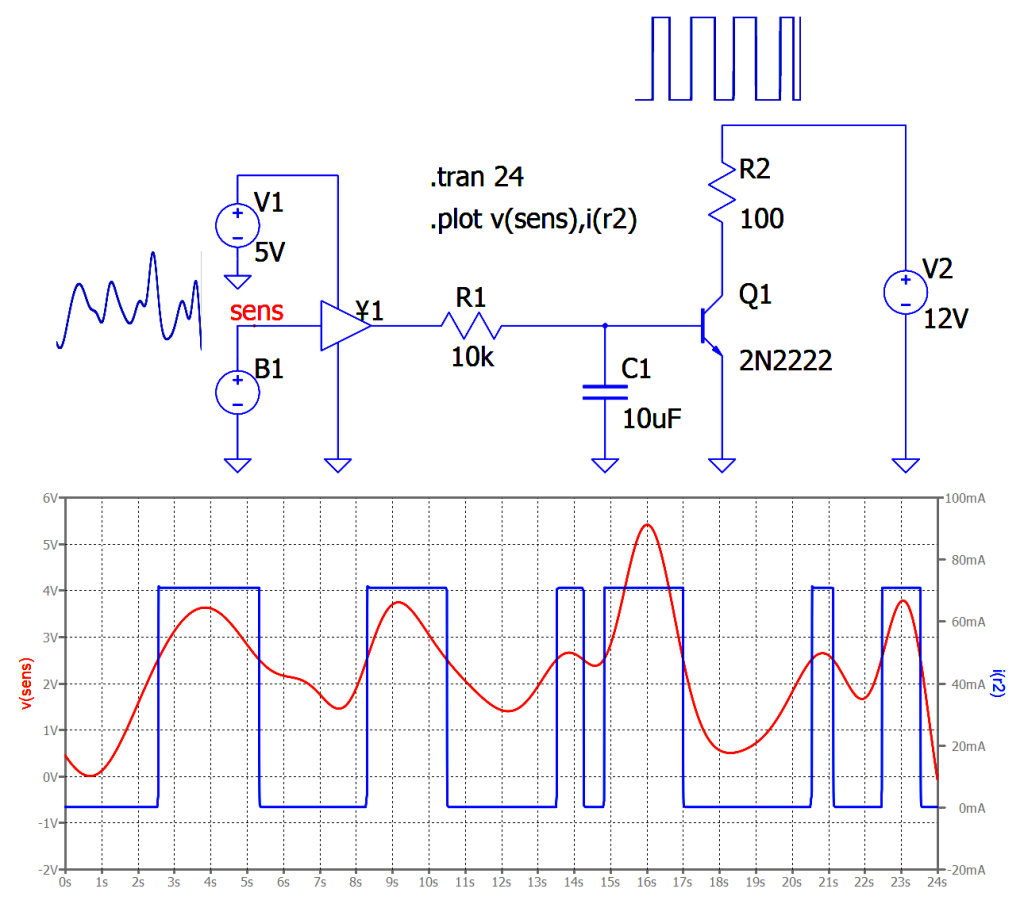

下一个示例涉及一种解决方案,当环境温度(通过假设的模拟传感器测量)超过某个阈值时,该解决方案涉及打开冷却系统。当温度降至阈值以下时,相同的冷却系统(由简单电阻器表示)关闭。该示例不考虑磁滞。如图 3 所示,该系统由电源系统、负载驱动电路、温度传感器和代表实际冷却系统的电气负载组成。发生器 B1 是通过复杂的数学公式模拟温度传感器在 24 小时内记录的电压的发生器。

从电路图中可以看出,来自温度传感器的模拟信号介于 0 V 和 5 V 之间,进入数字缓冲器的输入端,将输出平方为 0 V 或 5 V 的数字值。通过这种平方操作,信号不再具有模拟分量,而只有由两个不同的电压值(0 V 和 5 V)形成的数字响应。为了获得更好的信号平方,可以使用 Schmitt 触发器。然后,数字缓冲器的输出驱动

晶体管以控制冷却系统。该图显示了温度传感器测得的信号电平(红色图)和流经负载的电流,完全平方(蓝图)。

图 3:模拟系统的原理图由电源、控制电路、温度传感器和风扇组成

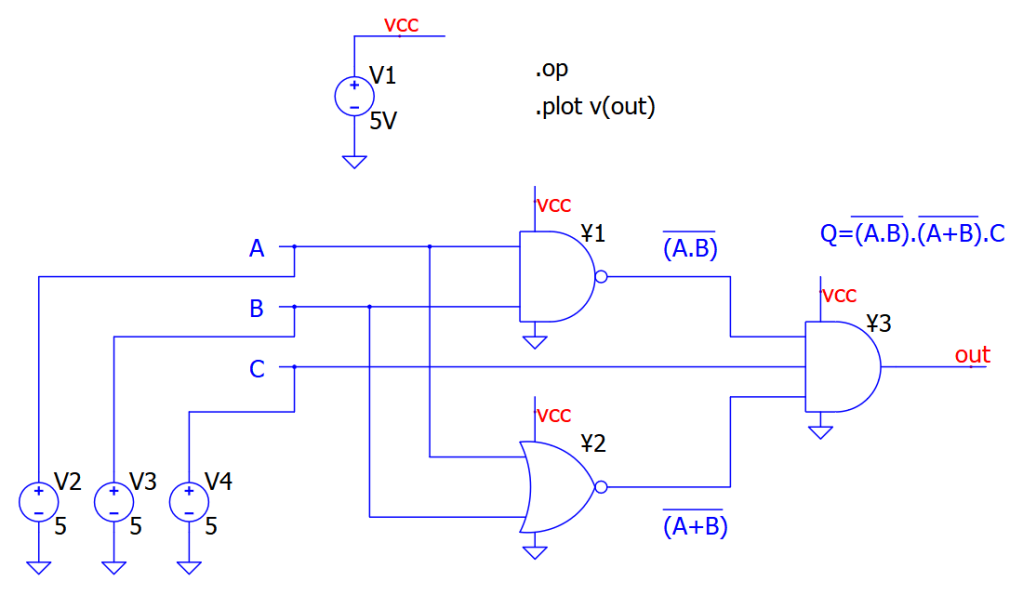

组合电路

组合电路是包含不同类型逻辑门的数字逻辑电路。换句话说,不同类型的逻辑门(如 AND、OR、NOT、NAND、NOR、XOR 和 XNOR)组合在一起,以创建执行特定操作的逻辑网络。它们 output 的 logic state 取决于 inputs 的每个 logic level,根据的条件组合确定终结果。这些电路没有内存,这意味着输出完全由电流输入决定,而不是由以前的状态决定。有时,根据使用的 logic gate 数量及其互连的复杂性,会创建极其复杂的配置。

复杂性可能会变得如此之高,以至于需要特殊的数字

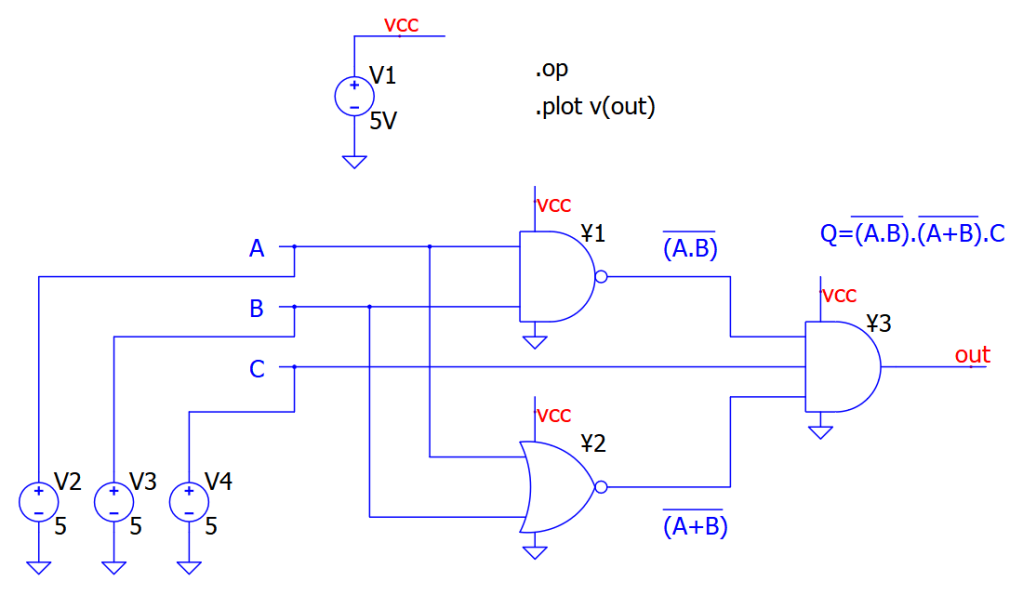

仿真器和逻辑分析仪来分析和求解这些逻辑网络。这些工具使我们能够验证电路的正确功能,识别任何设计错误并优化性能。图 4 中的逻辑图显示了一个由三个输入组成的组合逻辑网络,这会产生 8 种不同的输入信号组合。它由一个 NAND 门、一个 NOR 门和一个 AND 门组成。所有可能的输入信号的组合产生了以下真值表。

该图显示了组合电路的输出如何根据输入的不同状态而发生显著变化。电路中的每个 logic gate 都执行一个特定的功能,有助于整体结果。例如,NAND 门仅在其所有输入都为高电平时产生低输出,而 NOR 门仅在其所有输入均为低电平时产生高输出。另一方面,AND 门仅在其所有输入都为高电平时产生高输出。

图 4:组合电路

分析组合逻辑网络需要全面了解逻辑门之间的交互以及这些交互对电路输出的影响。随着输入和逻辑门数量的增加,复杂性呈指数级增长,因此设计和验证工具必不可少。使用数字仿真器,可以对电路在各种场景中的行为进行建模,确保它们在所有预期条件下都能正常工作。组合电路是数字逻辑的基本组成部分,对于实现广泛的

电子应用至关重要。在本例中,输出始终等于逻辑 0,除非逻辑门假设值为 A=0、B=0 和 C=1。

因此,我们创建一个新项目(参见图 2 中的电路图),并从“Behavioral”和“Gates”组中添加逻辑门“5-Input AND 门”。定位逻辑门后,需要定义电路的输入和输出以及电源触点。输入可以连接到代表逻辑信号(0 和 1)的方波电压源。逻辑门的输出可以连接到负载电阻器,可以在负载电阻器上测量电压。五个信号发生器产生电位为 0 V (L) 和 5 V (H) 的方波。分析刚刚创建的系统的逻辑操作,我们可以查看输入和输出信号的波形,从而验证逻辑操作的正确性。如图所示,生成所有可能的信号组合,然后将其输入到逻辑门的相应输入中。

因此,我们创建一个新项目(参见图 2 中的电路图),并从“Behavioral”和“Gates”组中添加逻辑门“5-Input AND 门”。定位逻辑门后,需要定义电路的输入和输出以及电源触点。输入可以连接到代表逻辑信号(0 和 1)的方波电压源。逻辑门的输出可以连接到负载电阻器,可以在负载电阻器上测量电压。五个信号发生器产生电位为 0 V (L) 和 5 V (H) 的方波。分析刚刚创建的系统的逻辑操作,我们可以查看输入和输出信号的波形,从而验证逻辑操作的正确性。如图所示,生成所有可能的信号组合,然后将其输入到逻辑门的相应输入中。 图 2:在 AND 逻辑门中,只有当所有输入都具有高逻辑值时,输出才会假定高逻辑值

图 2:在 AND 逻辑门中,只有当所有输入都具有高逻辑值时,输出才会假定高逻辑值