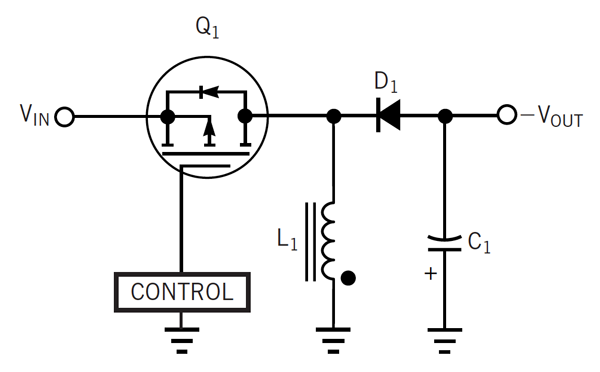

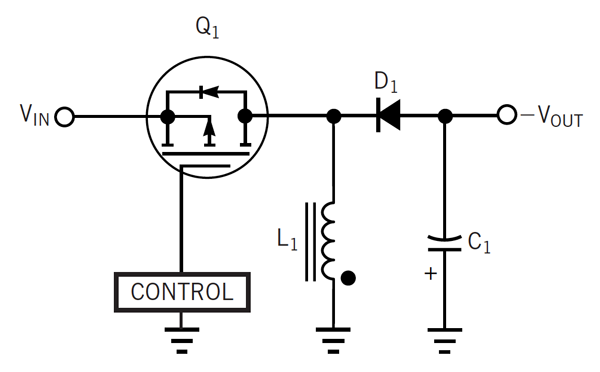

许多电子系统需要正电压和负电压才能正常运行。从较高电压输入生成高效、低压正输出通常需要使用同步降压稳压器。但是,当从正输入电压生成负输出电压时,通常会使用反激式拓扑,尤其是在输出电流较高的情况下。同步降压和负反激式(也称为降压-升压)的操作和控制特性存在显着差异。图 1显示了负反激电路所需的基本组件。

反激式拓扑产生负输出电压图 1该反激式拓扑从正输入产生负输出电压。

当 FET Q 1导通时,输入电压出现在电感器 L 1两端,此时没有输入电流流向负载。此时传递到负载的所有输出电流都来自输出电容C 1,因为

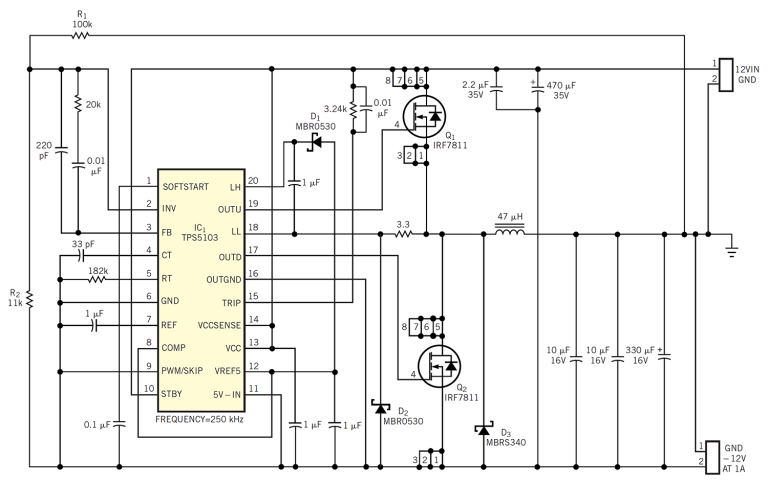

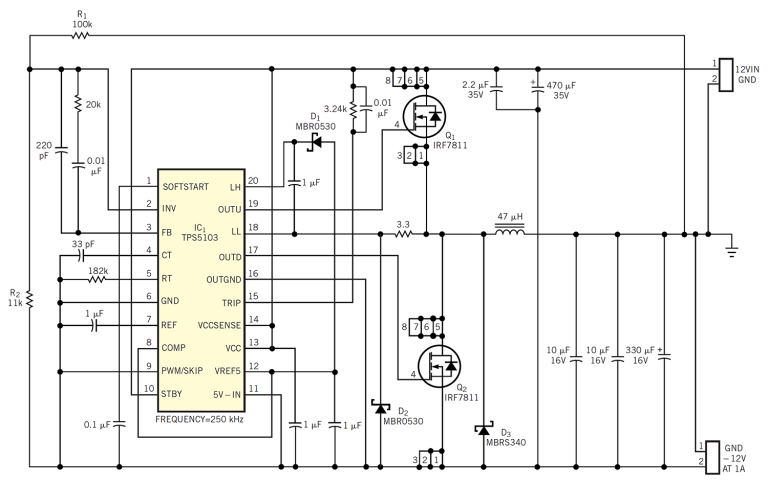

二极管D 1是反向偏置的。电感器中的电流持续增大,直到控制电路确定关闭 FET Q 1 的适当时间。此时,电感器 L 1两端的电压极性会反转,以试图维持电流流动,从而将电感器的顶侧相对于地拉至负值并迫使二极管 D 1导通。输出电压变为负值,处于电感器电压的二极管压降范围内。 控制电路工作的占空比也不同于同步降压的占空比。尽管同步降压的工作占空比为 D=V OUT /V IN,但负反激式的工作原理为 D=V OUT /(V OUT –V IN )。例如,如果所需输出电压是输入电压的一半,则同步降压以 50% 占空比运行,而负反激式以 33% 占空比运行。图 1 中的简单负反激电路与图 2中的同步降压控制器负反激电路之间的比较非常简单。

同步降压控制器图 2同步降压控制器构成了该负反激式配置的。

在图 2 中,FET Q 2反映了图 1 中二极管 D 1的功能,但二极管中出现的正向压降有所减少。这种较低的下降显着提高了效率。当 FET Q 1和 Q 2均截止时,二极管 D 3在短死区时间内导通,从而进一步降低损耗。反馈电压通过

电阻器R 1出现在输出地,因为控制电路以负输出电压为参考。 R 2通常将输出电压设置为所需水平,因为它不会像改变 R 1那样改变反馈补偿网络。输入电压、输出电压或两者的所需改变可能需要改变电感值。电感值为:

请注意在此类实现中使用控制器的某些限制。由于控制电路以负输出电压轨为参考,因此控制器的输入电压额定值必须大于 V IN +|V OUT |。控制器还必须达到 V IN(值)额定值,该值在系统加电时输出电压为零时发生。在宽输入电压范围内运行的控制器通常效果。

阅读更多设计理念FET 的漏源额定值还必须能够承受 V IN +|V OUT |,并且 FET 承载的峰值电流大于输出电流的两倍。低电阻、快速

开关 FET 产生的损耗。高效率是该电路的主要优点。由于该电路使用 n 沟道 FET,而不是更高电阻和更昂贵的 p 沟道部件,因此该电路可实现大于 90% 的峰值效率。