些以更高速度运行的众多时钟使噪声和干扰成为可靠系统运行的一大问题。在本文中,我们将讨论精心设计的集中式时钟源如何使用可编程时钟

发生器来解决时序设计问题,同时限度地减少信号衰减并防止噪声干扰。

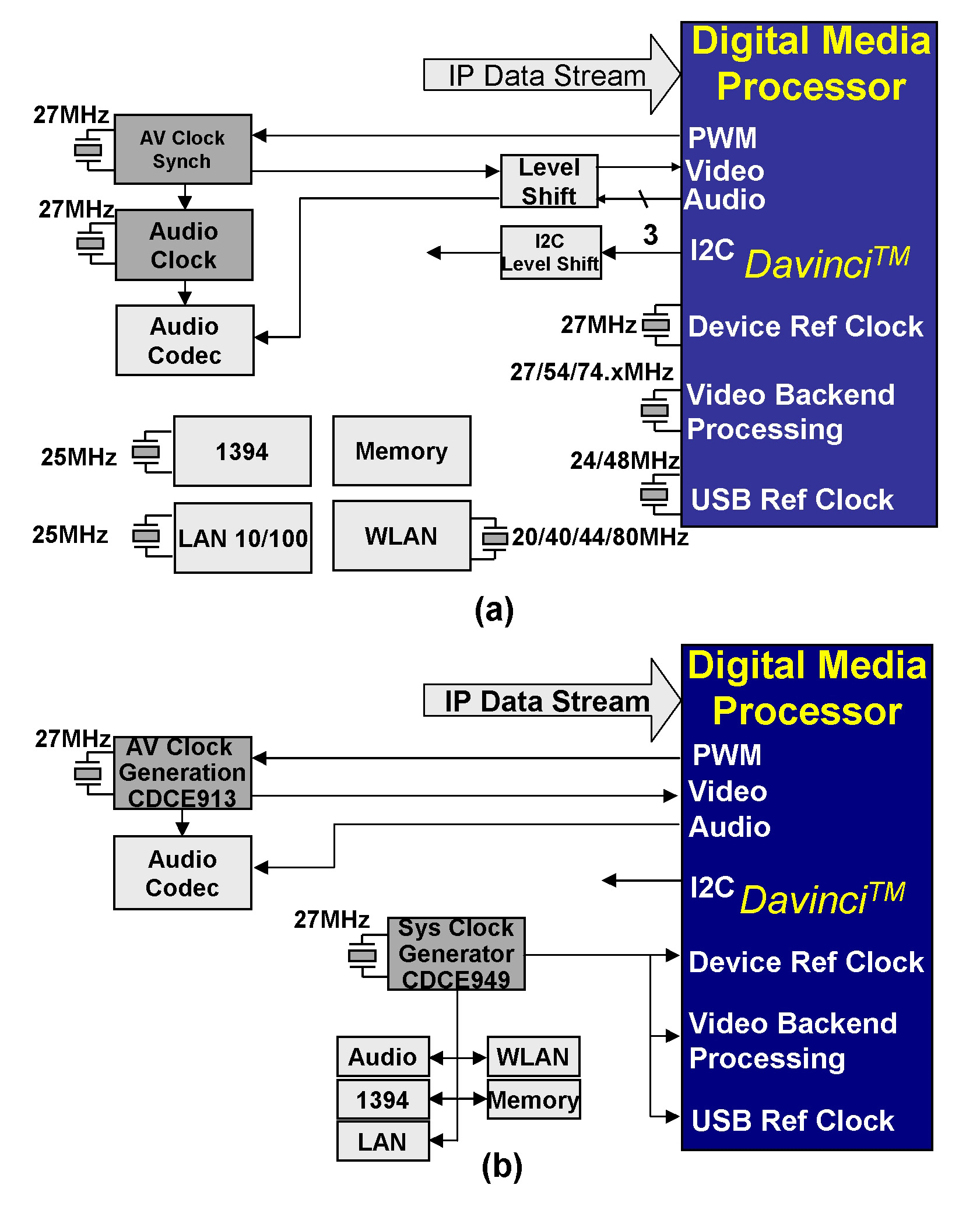

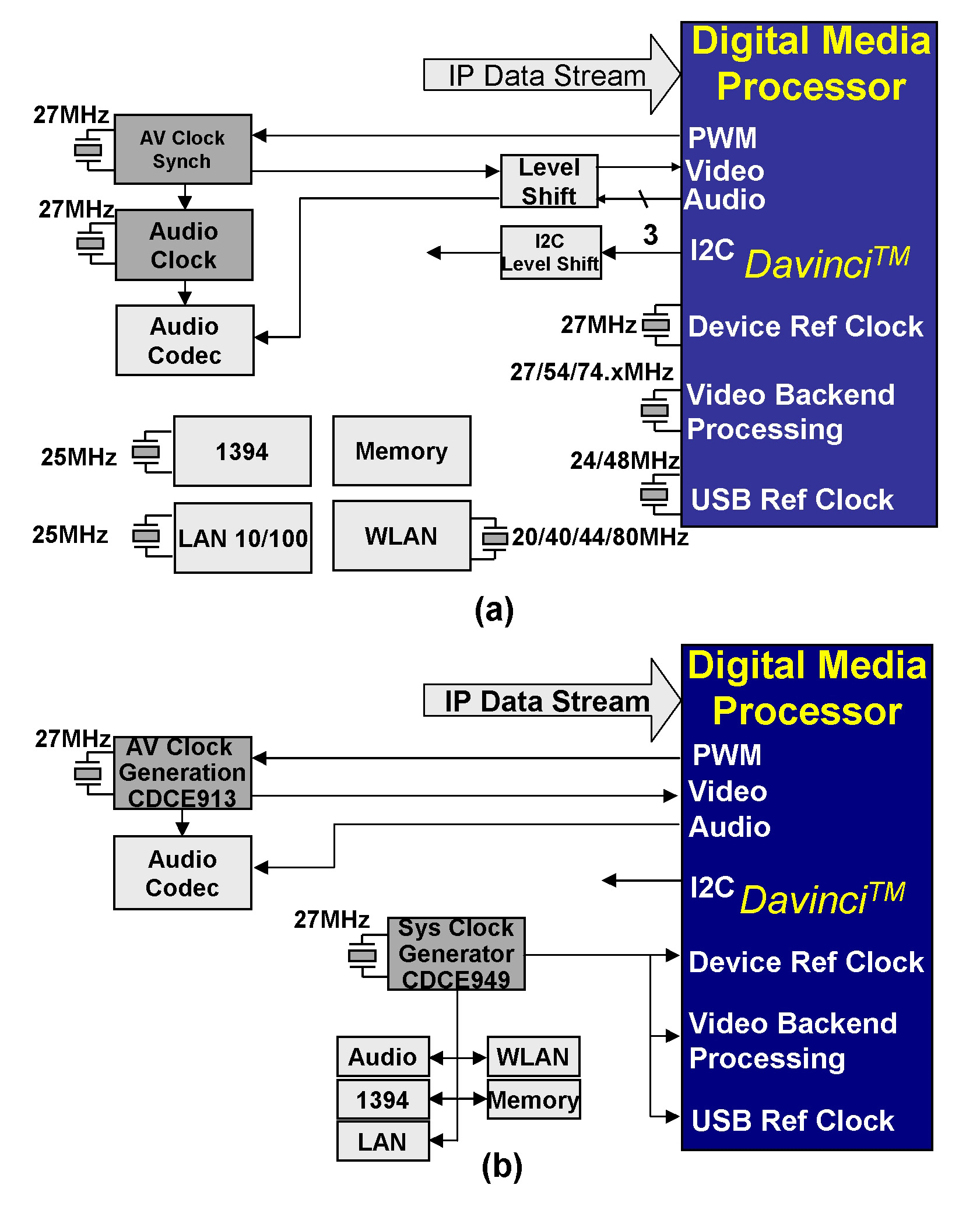

除了系统性能之外,更快的上市时间、更低的总体成本、更简单的库存管理和更少的未来升级投资等因素也是选择时序解决方案的主要决策因素。因此,商品化设计方法被广泛采用,以便大量重复使用研发 (R&D) 资金,并提供灵活性以快速适应未来的平台变化。基于锁相环 (PLL) 技术的可编程时钟发生器可以提升这些业务能力。 作为数字媒体系统的示例,图 1 示出了 IP 机顶盒的框图。

图 1:IP 机顶盒时钟树

(点击图片放大)

该系统有三种类型的功能模块:

1)处理器——DSP(例如Davinci)、ASIC或FPGA;

2)音频编解码器;

3)接口。

有十多个模块需要不同频率的参考时钟。其他数字媒体系统(如高清电视 LCD 面板)具有类似的时序复杂性。

传统

晶体振荡器方法

传统上,参考时钟是用晶体

振荡器在本地生成的(图 1a)。这种方法的优点是可以将时钟源放置在非常靠近其驱动的组件的位置,以简化布线。此外,它不易受干扰,因此具有更好的信号完整性。

此外,不同供应商提供的标准频率种类繁多,使得单价非常低(每台成本远低于 0.50 美元)。但是,随着端口或模块数量的增加,我们在使用这种“本地”方法时会遇到一些明显的缺点。

累计晶体成本会上升,尤其是当需要 40 MHz 以上的频率时。随着制造成本的增加,高频晶体振荡器的成本很容易超过 1.00 美元。晶体所需的电路板空间也会增加。此外,无法同步模块之间的时序。

对于某些设计来说,当调试变得困难时,这种情况是不可取的。更重要的是,这种离散时钟解决方案灵活性很差,使得系统难以重新配置参考时钟以进行测试、接口电源管理、以后升级或降级端口或模块,以及在多个平台上重复使用。

基于石英的设备故障率较高。晶体容易老化(每年±2 至±5 ppm)。频率随温度漂移。整个电路板的温度分布不均匀会导致频率之间出现不同的漂移量。显然,晶体数量的增加会增加故障率,并需要更多的工作。这也意味着成本增加。

从采购角度来看,减少不同元件的数量具有明显的好处。这提高了上市时间和交付方面的竞争优势,并且在将同一器件用于多个批量设计时提供了更大的议价能力。这些缺点使得分立晶体振荡器方法不受欢迎。

基于 PLL 的集成可编程时钟的优势

本地晶体方法的替代方法是使用集成可编程时钟发生器(图 1b)。本例中使用了 CDCE949 和 CDCE913。CDCE949 多可以生成九个不同的时钟,而 CDCE913 多可以生成三个不同的时钟。这种集中式方法大大减少了分立板元件的数量,包括晶体以及使用分立晶体时用于电平转换的设备。

基于 PLL 的时钟发生器通常包括四个主要功能块:

1)用于任意速率频率生成的多个 PLL;

2)输入电路;

3)输出缓冲器;

4)可编程控制块(I2C、SPI、EEPROM 或引脚控制)。

除了产生正确的频率外,集成解决方案还可以实现许多功能来提高系统性能。明显的好处是灵活性。

当 PLL 以小数 N 分频模式运行时,它只需要一个非常低成本的标准晶体作为输入,并生成宽范围内的任何频率。例如,CDCE949 支持从DC到 230 MHz 的输出频率。使用多个 PLL,您只需使用一个设备即可以同步方式生成所有所需频率。当发生频率漂移时,PLL 可确保所有输出都朝同一方向漂移。更少的设备意味着更高的可靠性、更低的成本和更好的库存控制。

这些时钟发生器提供的可编程性有助于不同的开发阶段。在原型设计期间,可以通过 I 2 C、SPI 或 SMbus 等方式动态调整频率。一旦设计确定,可以通过 EEPROM、控制引脚或金属掩模更改来维护设置,以限度地降低批量生产期间的成本。当将来需要更改时,可以对同一设备进行重新编程,而无需更改电路板布局。

然而,当使用集成时钟发生器时,在电路板上分配具有良好信号完整性的时钟可能是一个挑战。通常,主板或媒体系统的时钟走线长度在 3 到 9 英寸范围内。对于这种走线长度,LVCMOS 信号可以以高达 200 到 300 MHz 的频率运行。两个实际问题是:

1)抖动:尽量减少由于长 PCB 走线导致的上升/下降时间劣化,以保持接收器处良好的抖动性能

2)EMI:防止同一板上的时钟信号之间耦合的噪声干扰。

限度地减少信号衰减,提高抖动性能

时钟信号的上升/下降沿需要很锐利,以实现低抖动性能。这意味着边缘由许多高频分量组成。电路板走线材料具有衰减效果,其作用类似于低通

滤波器。频率越高、走线越长,衰减量就越大。当信号到达接收器时,不同的频率分量会以不同的方式衰减,导致边缘失真,使其更容易受到抖动的影响。 减少上升/下降时间恶化的一个简单有效的方法是通过源和接收器的阻抗匹配。图 2 描述了通过在

驱动器(或时钟输出引脚)和接收器的输入引脚之间插入终端电阻 Rs 来实现阻抗匹配的两种不同情况。

图 2:点对点和多点的阻抗匹配

(点击图像放大)

图 2a 是点对点的情况,图 2b 是多点的情况。50 Ω 走线通常用于高速信号传输。已知驱动器的上拉和下拉等效阻抗通常在 15 至 20 Ω 范围内,R s的值 计算如下:

1) 对于点对点:R s =Z o -R o,其中R o 是驱动器等效阻抗

2) 对于多点:R s =Z o -N×R o,其中R o 是驱动器等效阻抗,N是接收器的数量。

终端电阻 Rs 应靠近驱动器放置,K 应小于一英寸。对于低于 40 MHz 的时钟频率,经验数据显示,LVCMOS/LVTTL 的走线长度 L 可达 13 英寸,具体取决于负载条件。

对于 100 MHz 左右的时钟频率,走线的长度可达 9 英寸。当频率更高时,时钟走线长度应进一步缩短。K、L 和 R s的值 可以通过实验或仿真进一步调整,以包括寄生影响。如果驱动器和接收器距离不超过两英寸,则不需要 R s。