4 个具有多个栅极连接的模块使用公共栅极驱动器电路时,减少辅助源连接中流动的任何电流非常重要。

图 1 在两个模块的简化示例中显示了辅助源连接如何为主电流路径提供自然的并行传导路径。一些电子(我们称之为“青少年电子”,因为它们喜欢走与其他电子不同的路径)可以流过此辅助源并行路径。该电流可能大到足以引起栅极振荡,甚至熔断模块内部的辅助键合线。

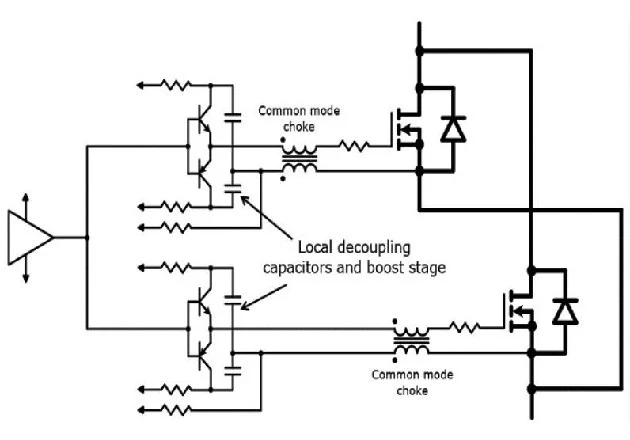

图 2 所示的电路用于减少这些不需要的环流。它是共模扼流圈的组合,共模扼流圈对输入和输出电流相等的正常栅极电流表现出低阻抗,但对仅在源极连接中流动的不需要的源极电流表现出高阻抗。除此之外,每对器件栅极连接都使用单独的局部升压级。这允许源极连接中存在电阻,但是,使用局部电容器,流经此路径的任何电流都不会影响栅极波形。如果仅使用简单的源电阻,情况就不是这样,因为流经该源电阻的任何电流都会影响栅极源电压,从而降低直接控制水平并增加栅极振荡的可能性。 图 2:栅极驱动器电路

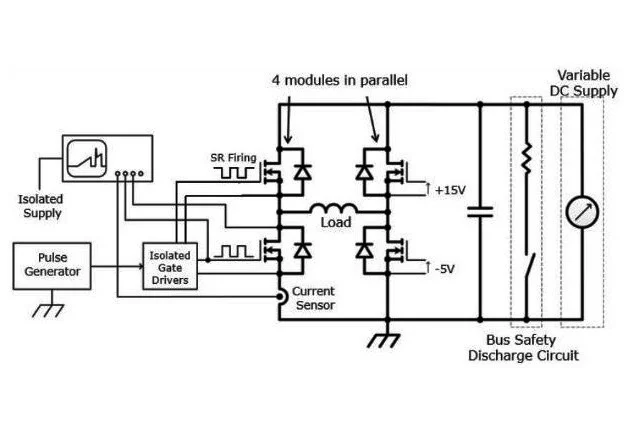

图 2:栅极驱动器电路 图 3:双脉冲测试 (DPT) 示意图

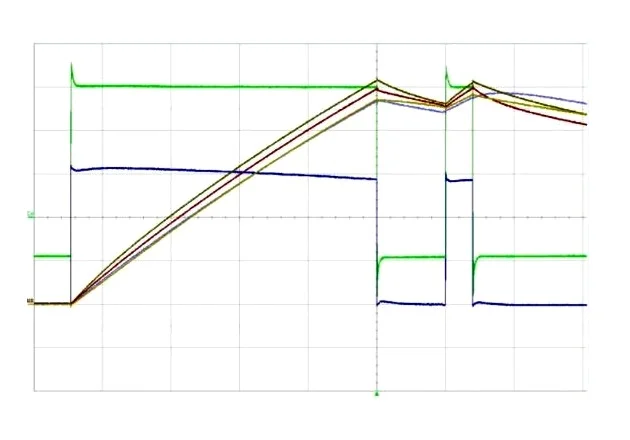

图 3:双脉冲测试 (DPT) 示意图 图 4:4 个并联模块的 DPT 电流波形(50 ?s/分度和 50 A/分度)绿色 Vgs 5 V/分度。蓝色 Vds 100V/分度

图 4:4 个并联模块的 DPT 电流波形(50 ?s/分度和 50 A/分度)绿色 Vgs 5 V/分度。蓝色 Vds 100V/分度 图 5:4 个并联模块的 DPT 电流波形(50 ?s/格和 50 A/格)

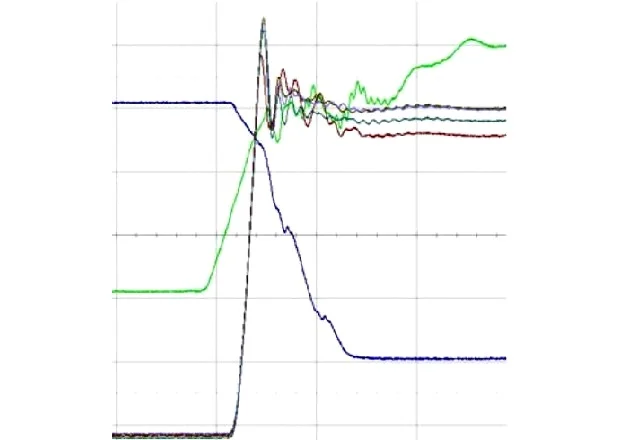

图 5:4 个并联模块的 DPT 电流波形(50 ?s/格和 50 A/格) 图 6:4 个并联模块的 DPT 关断波形(200 ns/分度和 50 A/分度)绿色 Vgs 5 V/分度。蓝色 Vds 100V/分度

图 6:4 个并联模块的 DPT 关断波形(200 ns/分度和 50 A/分度)绿色 Vgs 5 V/分度。蓝色 Vds 100V/分度 图 7:4 个并联模块的 DPT 开启波形(200 ns/分度和 50 A/分度)绿色 Vgs 5 V/分度。蓝色 Vds 100V/分度。

图 7:4 个并联模块的 DPT 开启波形(200 ns/分度和 50 A/分度)绿色 Vgs 5 V/分度。蓝色 Vds 100V/分度。免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。