的宽带隙 (WBG) 半导体在高电压下具有超快速切换和低损耗,已接近理想状态,而现代 MOSFET 和沟槽 IGBT 也可以显示高 dV/dt 和 di/dt 水平。然而,“低侧”电路中的快速切换可能会将瞬态电压耦合到栅极驱动电路,导致操作混乱或损坏,而“高侧”栅极驱动器还会受到信号和电源隔离的压力。本文研究了这些影响并解释了如何减轻这些影响,以及评估压力和损坏(特别是局部放电 (PD))的实验结果。

现代半导体

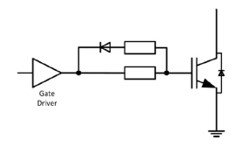

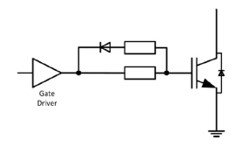

开关采用宽带隙 (WBG) 技术,甚至 MOSFET 和一些 IGBT,能够实现极快的开关速度。这减少了开关转换期间的耗散,从而允许以高效率、更高功率密度、更小的无源元件和更低的成本实现更高频率的操作。然而,由于 dV/dt 和 di/dt 水平较高,因此存在增加 EMI 和对栅极驱动绝缘系统施加压力的缺点。 图 1 显示了 IGBT 的典型栅极驱动电路,施加 5V 至 20V 之间的正电压以打开器件,施加 0V 以关闭器件。静态上,该电路也非常适合 SiC 和 GaN 技术中的增强型 Si MOSFET 和 WBG 器件 - 在所有情况下,只要施加连续栅极 0V,器件就能保证关闭。

图 1:简单的栅极驱动电路

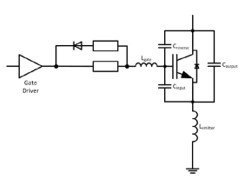

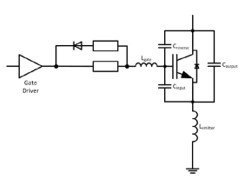

然而,当器件快速切换时,就会出现问题,寄生电容和电感元件(如图 2 所示)就会发挥作用。如果我们以漏源电流的 di/dt 值为 10A/ns(这在的 GaN 器件中是可行的)和源电感为 15nH 的情况为例,根据 V = - L di/dt,电感器两端会出现 150V。在开关关闭时,电压将源极拉向负极,与栅极驱动相反;在开关打开时,方向为正,再次与栅极驱动相反。 其后果可能是效率损失,甚至由于虚假开启导致击穿而造成损坏。15nH 可能看起来很大,但仅代表约 25mm 的 PCB 轨道。即使是 PCB 通孔也有约 1.2nH 的电感,产生 12V 的瞬态电压。实际上,在这些高 di/dt 水平下,只有芯片级封装才是实用的,使用开尔文连接到栅极和源极以进行栅极驱动。当无法避免某些电感时,用负电压驱动栅极以达到关断状态会有所帮助。

图 2:含有寄生元件的栅极驱动

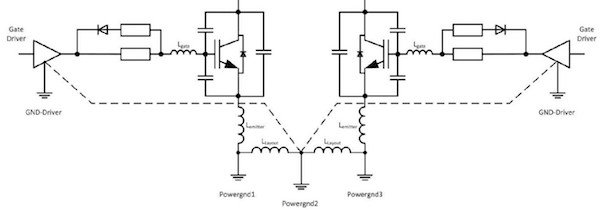

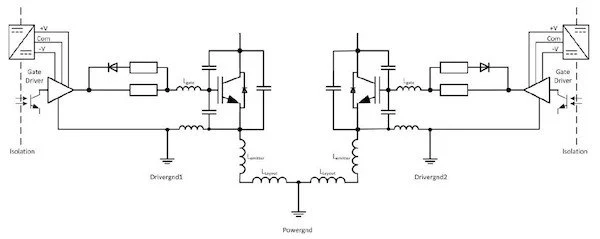

在实际电路中,例如

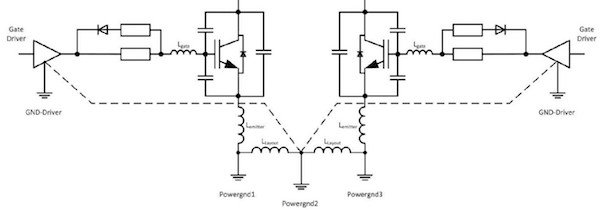

逆变器或电机控制中的推挽式或全桥式电路,两个低侧器件通常共享源极和栅极驱动电流的公共回路,如图 3 所示。

图 3:共享公共接地的低侧器件

现在无法进行开尔文连接,因为有两个驱动器,每个驱动器都有自己的回路。两个驱动器接地和两个发射极(源极)连接必须连接在一起,如果这个点在物理上位于 Powergnd 1,靠近左侧开关,则右侧开关的源极连接电感将比左侧开关大,从而导致不对称切换、潜在的 EMI 和电感两端的感应电压造成的损坏。为了实现对称,点“Powergnd 2”是的选择,但这是一个糟糕的折衷方案,因为现在两个源极在栅极驱动环路中具有相等但较大的连接电感,特别是在设备可能物理上不接近的高功率系统中。

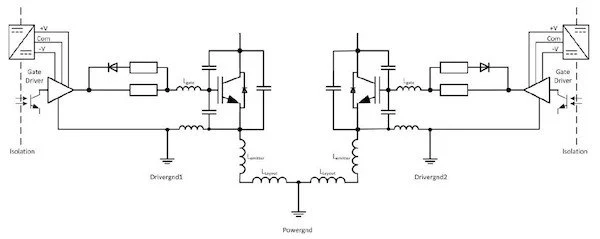

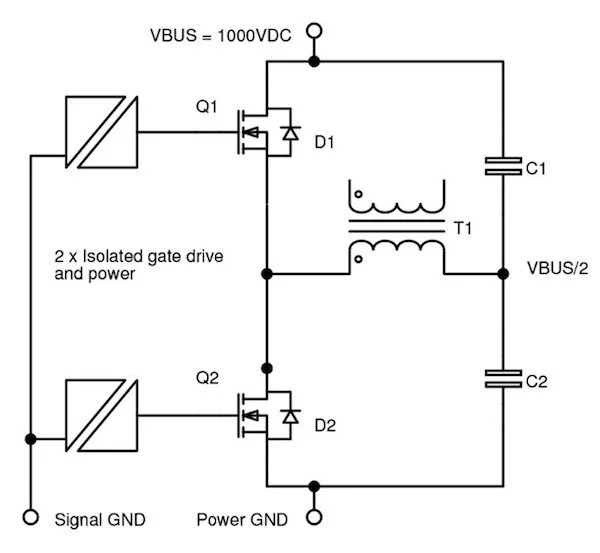

一种解决方案是向两个栅极驱动器提供隔离的信号和电源,如图 4 所示。现在,驱动器信号和电源返回可以直接连接到它们各自的设备发射器(源),从而排除驱动环路中的大多数外部电感。 高端开关挑战 图 4 的布置解决了 di/dt 导致发射极(源极)电感产生栅极电压瞬变的问题。它通常也用于“H”桥中的两个“高端”开关,其中两个栅极驱动回路实际上是反相开关节点,因此必须相互隔离。 在高端配置中,高开关电压现在出现在栅极驱动隔离元件上,并可能导致其他问题。根据 I = C dV/dt,高 dV/dt 是可能通过隔离电容的位移电流安培数的问题。由于边缘速率很容易达到 100V/ns,10pF 屏障电容将通过一安培电流,流经栅极驱动电路的初级,可能会中断操作。

图 4:采用开尔文连接进行信号和电源隔离的栅极驱动器 栅极驱动信号隔离元件通常是

光耦合器或

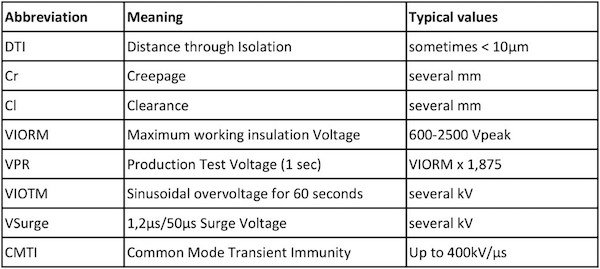

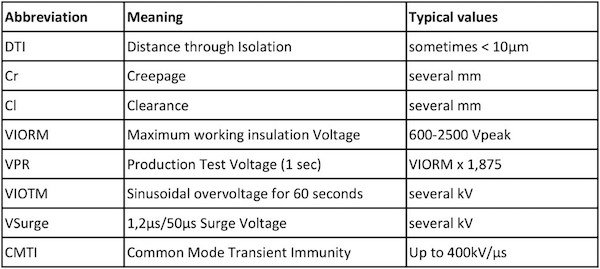

变压器,有时也使用电容耦合。隔离栅极驱动器 IC 的性能由表 1 中的关键参数给出,其中 CMTI 是与我们的高 dV/dt 电路相关的共模瞬态抗扰度。然而,这个值是实验室测量值,很可能是单脉冲。没有提到持续高压、高 dV/dt 波形的可靠性。、

表 1:隔离栅极驱动器的关键参数

其他参数 VIORM/VIOWM/VIOTM/VPR 也很重要,但同样与我们的开关电路没有直接关系,因为标准测试通常定义为 50/60Hz、DC 或峰值。单独的栅极驱动变压器具有与规格类似的限制,通常只是简单的“高压”测试,持续一秒或一分钟,通常在某个 DC 电平或 50/60Hz 的 AC 下。很少能找到在绕组或甚至 CMTI 上施加的高频高开关电压下的可靠性评级。

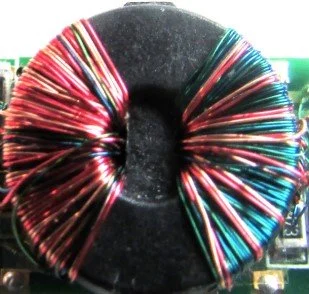

对于变压器,获得高绝缘的方法因应用而异;漆包线可以经受“高压”测试,但不可靠,漆层上几乎肯定会有针孔。安全机构当然不允许将其作为任何电压下的安全屏障。绝缘性更好的电线(如“三重绝缘”类型)可以获得安全机构的批准,但体积庞大,导致变压器具有相对较高的耦合电容和位移电流。

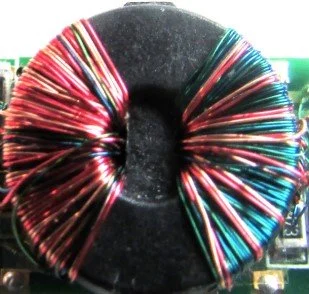

理想的结构是绕组通过空气以保证的距离进行物理分离,以满足安全机构的要求,提供低绕组间电容,并且不依赖可能会受到局部放电影响的固体材料。

完全相同的考虑也适用于隔离栅极驱动电源内的变压器,其中 CMTI 额定值通常会被省略,并且高压隔离会以多种方式指定。

局部放电效应 我们提到过局部放电 (PD),即固体绝缘材料在受到高压应力时缓慢退化。这种效应是由材料中微孔的连续分解引起的,如果材料是有机类型,则会导致等离子体碳化。空隙会造成性短路,降低有效的整体绝缘厚度,导致剩余绝缘层上的电压场强更高,终导致完全失控故障。PD 效应突然开始于“起始”电压,该电压取决于空隙中的气体、压力和空隙大小,并以“帕申”曲线为特征 [1]。对于切换电压,起始点还取决于频率。

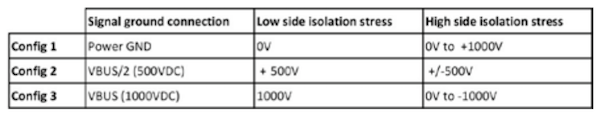

表 2:“BIER”测试配置 图 5:绕组之间具有物理隔离的栅极驱动变压器

图 5:绕组之间具有物理隔离的栅极驱动变压器 即使是块状材料的击穿电压也不应仅从表面来判断。例如,玻璃被认为是一种极好的绝缘体,其击穿电压约为 60kV/mm - 但这是 60Hz 时的击穿电压。在 1MHz 时,该数字不到该值的十分之一,约为 5kV/mm。由于某些栅极驱动 IC 的绝缘距离小于 10μm,因此需要仔细考虑高频效应。因此,开关电压水平、dV/dt 和频率是评估绝缘可靠性的关键参数。还应评估由于过冲和寄生电容和电感谐振而产生的瞬态电压,并将其添加到系统电压中。

图6:PD测试评估电路

屏障绝缘评估与研究

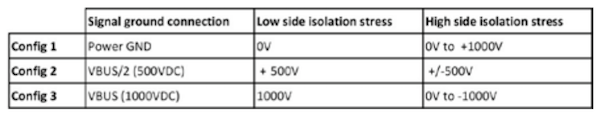

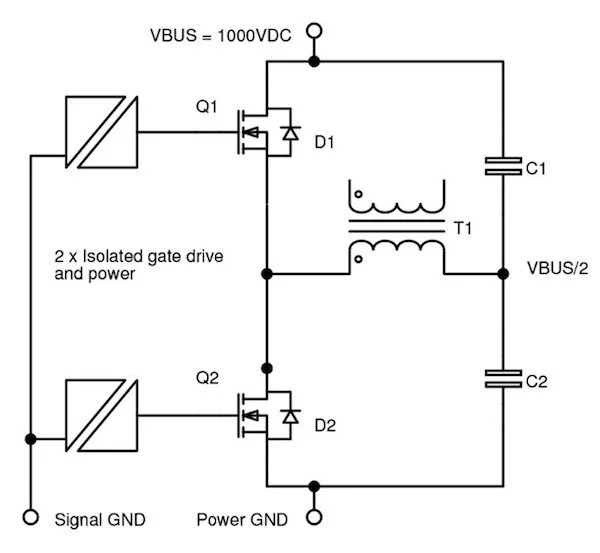

栅极驱动电源制造商 RECOM [2] 已经意识到 DC-DC 转换器产品中的变压器在高开关共模电压下存在潜在问题,并与格拉茨工业大学和约翰内斯堡应用技术大学的绝缘材料 Priv.-Doz. Dipl.-Ing. Dr.techn. Christof Sumereder 合作开展了一项研究。这项工作的内部代号为“BIER”(屏障绝缘评估和研究),包括对 30 个半桥功率级的评估,这些功率级专门采用隔离的高低侧开关构建,如图 6 所示。构建了三种不同的配置,如表 2 所示,并在 70°C 环境温度、1000V 直流电轨、50kHz 开关频率和 65kV/μs 边缘速率下运行 1464 小时。 PD评估结果

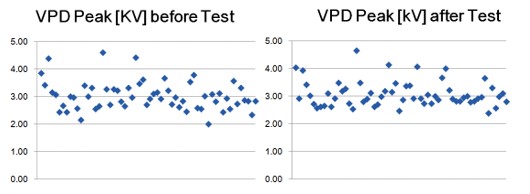

图7:PD评估结果

T1 不属于测试的一部分

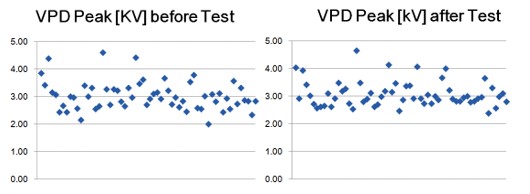

在测试运行之前和之后进行了局部放电测量,结果表明,在所用的配置中,性能没有明显下降(图 7)。局部放电起始电压保持在施加的峰值开关电压的两倍以上,表明裕度良好,并预测可靠的长期运行。完整可从 RECOM 网站 [3] 获取。

结论

推挽和桥式电路中栅极驱动器信号和电源的隔离解决了“低侧”和“高侧”电路中电压瞬变耦合到栅极的问题。然而,高侧隔离元件在高频和高边沿速率下仍然会受到高共模电压应力。实际局部放电测试表明,栅极驱动器 DC-DC 电源中的隔离元件可以设计为具有良好的长期可靠性。RECOM 拥有一系列 DC-DC 转换器,其输出电压和隔离额定值适用于 IGBT、SiC 和 GaN 技术的高侧栅极驱动器。