电源开关通常分布在器件指状物和

VIA 阵列中,并带有较大的金属布线以限制金属电阻。这种布线可能包括分布在多个金属层中的数百万个 VIA,这可能并不罕见。这使得开发一个简单的简化电阻模型变得具有挑战性。结合寄生参数提取和仿真工具可以利用强大的方法来模拟这些寄生参数。设计人员应该意识到,建模准确性通常会受到寄生参数提取速度和仿真时间的影响。通过以下建议,设计人员可以对集成

电源开关的电路验证准确性有更大的信心。

寄生参数提取工具

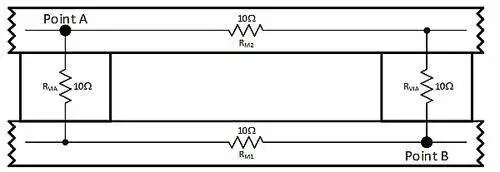

当使用寄生提取工具来模拟布线电阻时,可以使用各种 VIA 减少技术来限制其寄生网表的大小和复杂性。使用提取工具时必须小心,不要过度简化等效寄生电路。例如,考虑图 1 中从点 A 到点 B 的基本金属和 VIA 阵列网络电阻:

图 1:10 Ω 点 A 至点 B 等效电阻

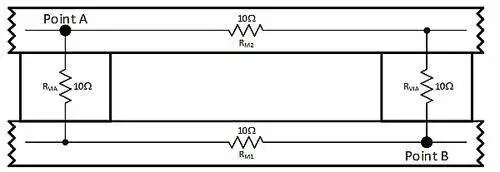

图 1 中 A 点到 B 点的等效电阻为 10 Ω 。但是,寄生提取工具提供的默认 VIA 减少技术可能会将这些平行 VIA 组合成位于阵列中点的“超级 VIA”。图 2 中所示的这种 VIA 减少技术可产生 15 Ω 的等效电阻:

图 2

图 2:15 Ω 点 A 至点 B 等效电阻

图 2 中的基本 VIA 减少示例与图 1 中的实际网络电阻相比,等效电阻相差 50%。设计人员必须理解并仔细权衡等效寄生网络表的准确性和大小之间的权衡。对于使用数百万个 VIA 的集成电源开关,可能需要额外的时间来创建准确的寄生模型。因此,建议在寄生提取期间禁用 VIA 减少。

此外,寄生参数提取工具通常提供电阻阈值,这样小于特定值的

电阻器就可以被忽略或减小/简化。虽然此选项有助于限制寄生网络表的大小,但这种减小会牺牲准确性。集成电源开关通常会尝试利用宽金属轨道和大型 VIA 阵列,从而导致非常小的电阻分布在非常大的网络上。准确的寄生参数提取需要考虑大量非常小的电阻。

仿真工具

同样,在对电源开关进行寄生验证模拟时,模拟工具可以忽略低于电阻阈值的电阻。同样,设计人员应该考虑准确性和模拟速度之间的权衡。分布在大型网络上的小电阻可能加起来足以抵消模拟结果的准确性。因此,建议设置较低的(或 0 Ω)电阻阈值。此外,将模拟公差缩小到模拟结果准确性变化可以忽略不计的程度。

仿真工具还可以提供专有的算法来帮助缩短仿真时间。尽管这些算法有时被宣传为、高性能的仿真选项,但它们通常通过以电阻阈值简化网表的复杂性来缩短仿真时间。与之前对这些电路缩减技术的担忧类似,仿真算法可能会降低寄生仿真模型的准确性。建议使用原生 SPICE 仿真算法来保持仿真结果的准确性。

图 1:10 Ω 点 A 至点 B 等效电阻

图 1:10 Ω 点 A 至点 B 等效电阻 图 2:15 Ω 点 A 至点 B 等效电阻

图 2:15 Ω 点 A 至点 B 等效电阻