使用高频QR控制器NCP1345设计双管反激240W USB PD3.1 EPR方案”继续更新,篇文章介绍了变压器匝比要求、PFC在不同的输入电压下的开通和关断要求、变压器设计等。本文将继续介绍初级辅助VCC电源设计、次级辅助VCC电源设计、初级输出高低边驱动、除PFC外的整体电路设计等设计问题,以及PCB Layout、方案中的其他器件选择等。

初级辅助VCC电源设计

由于输出电压的范围很宽几乎达到10倍,所以常规的用反激绕组供电变得非常困难,如果通过稳压电路给IC供电,由于输出电压范围非常宽那么又面临着较大的稳压电路的功率损耗。

所以在设计时部分考虑用正向绕组电压给VCC供电,由于PFC的输出电压为400V,而5V至12V输出时PFC停止工作,90VAC整流滤波后的直流电压大约120V, 所以电压与电压的比值约为3.33倍,远小于输出电压的变化范围,所以用正向电压绕组供电稳压电路上的损耗远小于反激绕组供电的损耗。由于输入电压是变化的所以正向绕组整流后的电压要经过稳压后才能给IC供电。

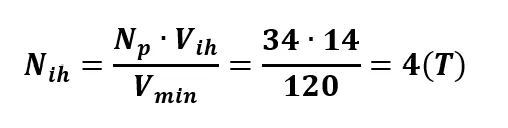

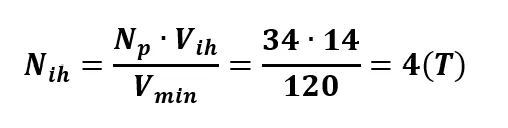

初级共设计有三个供电绕组,见图4:

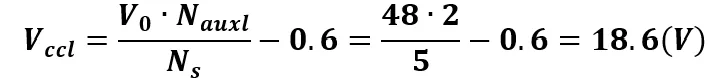

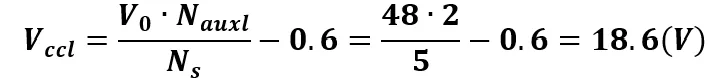

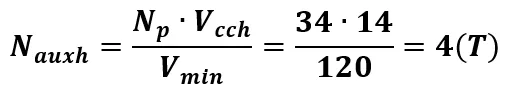

1.低边低压反激绕组auxl,用作ZCD检测及OVP用,同时在高压输出时给VCC供电。这个电压是给NCP1345之间供电所以不能超过NCP1345的VCCL端子的OVP值及GaN的VCC电压。输出48V共5T,那么取这个绕组2T,所以得到下列VCCL的电压:

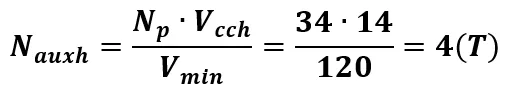

2.低边高压正向绕组Nauxh,当120VDC输入电压时这个正向绕组电压要有足够的电压给Vcch供电。这个电压选择设计14V左右。

Vmin=120V

Vcch=14V

3.高边浮动的电压给半桥驱动的高边供电,这个也是用正向绕组设计,当120VDC输入电压时这个正向绕组电压Vih要有足够的电压给半桥高边供电。同样地,这个电压选择14V, 那么得到高边浮动正向绕组ih的匝数:

图 4. 变压器辅助绕组电路示意图

次级辅助VCC电源设计

次级输出电压48V,一般的同步整流控制器没有这么高的电压定额,有两种供电方法:一是把48V通过稳压电路降低电压给IC供电;二是另加一个低压反激绕组给IC供电,通过电路使输出电压和辅助的绕组电压并联工作作电压切换,当输出高电压时由辅助绕组供电,当低输出电压时由输出电压供电,这样的好处是为了降低驱动损耗并效率。

所以次级辅助绕组设计为2T(见图4), 对应48V输出时的电压约为18.6V, 而两个电压的切换点对应的输出电压约为25V左右。

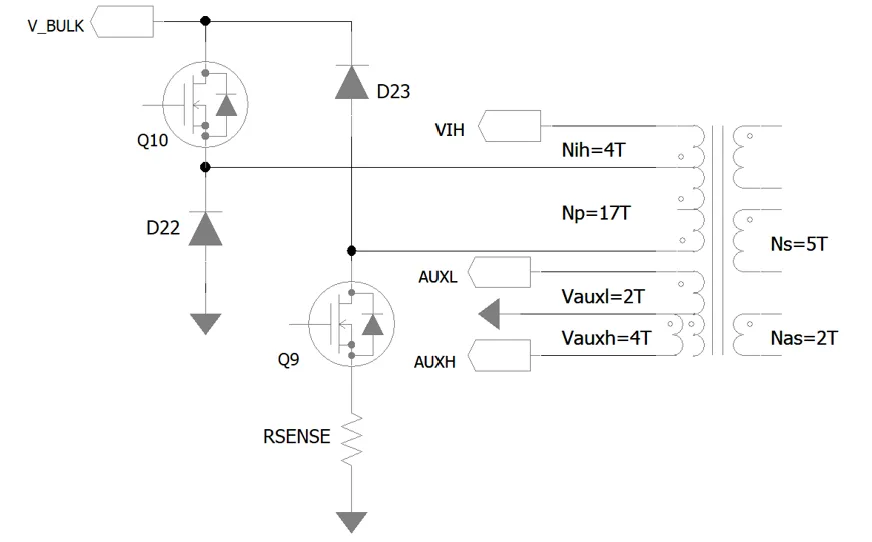

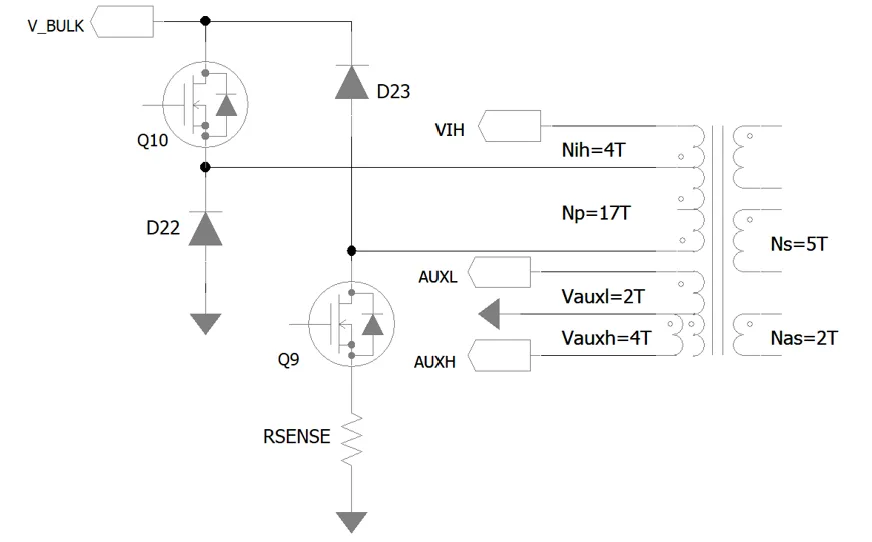

初级输出高低边驱动

双管Flyback需要额外的高边驱动,高边驱动可以用隔离变压器也可以用半桥驱动器。这里使用ONSEMI的NCP51530B半桥驱动器,高频低损耗且具有25nS的高边驱动延迟。为了使高低边的驱动延迟尽量一致,低边的驱动信号也经过驱动器并在驱动器的输出加一RC延迟电路使得高低边管导通时间尽量一致,见图5。

图5. 半桥驱动电路示意图

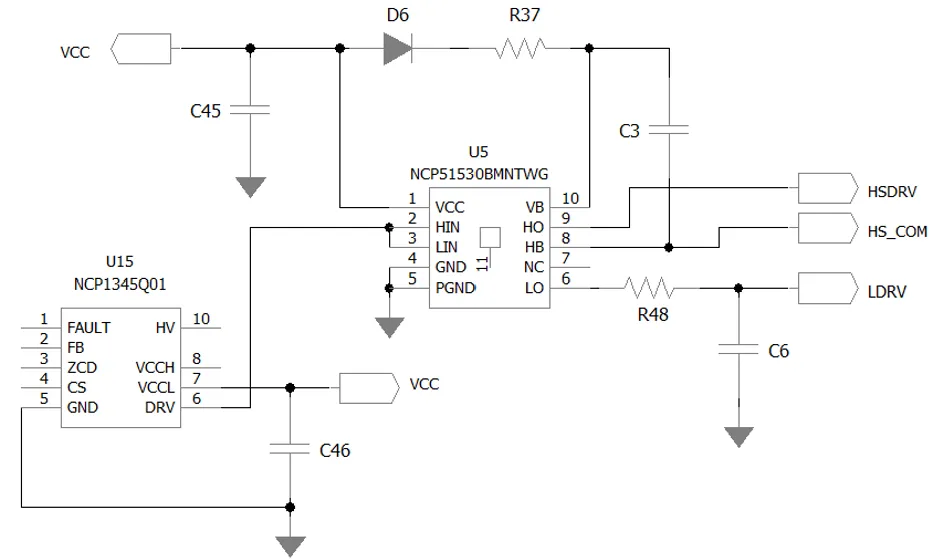

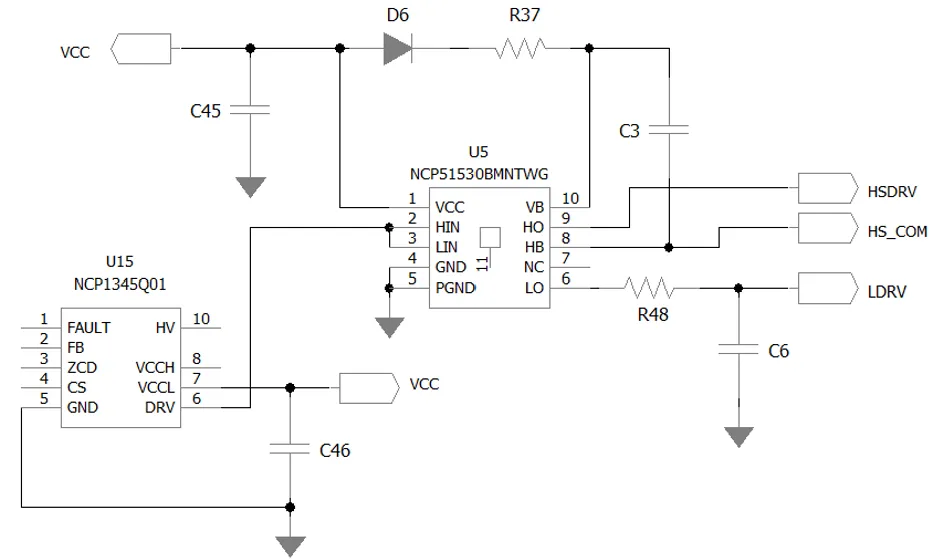

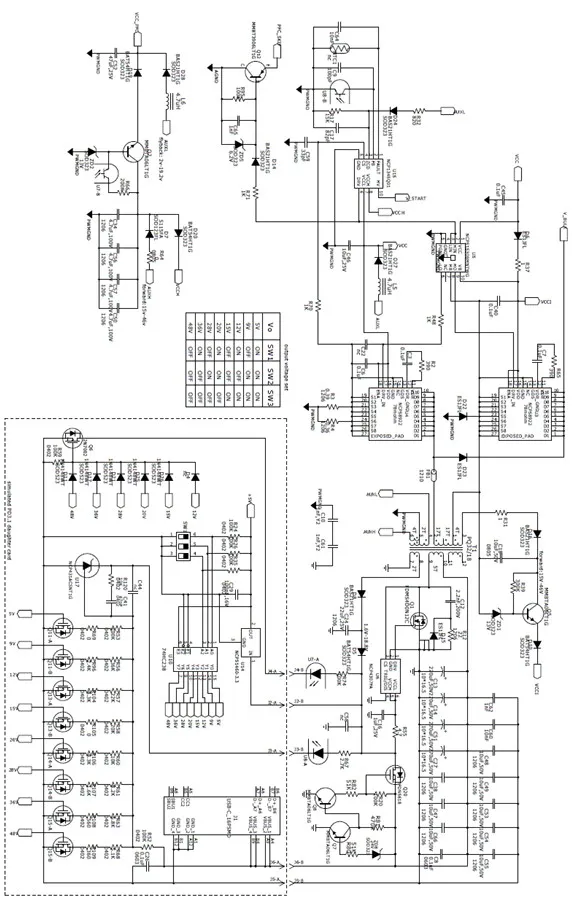

除PFC外的整体电路设计

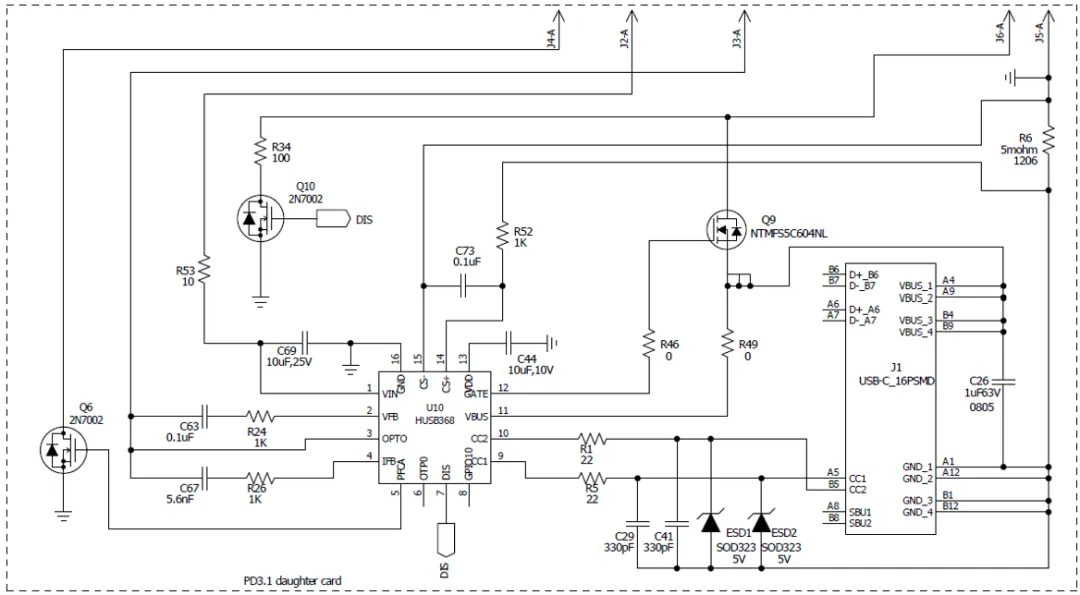

PD部分是单独设计一块子卡,本方案设计时由于没有适合的48V PD协议控制器,所以用分立器件设计了一块仿真控制卡来模拟PDO输出。控制子板具有标准的PD子卡接口信号,当有适合的PD协议控制器时很容易设计一块标准的PD卡。除PFC部分外完整的电路如图6所示.

图6. 除PFC部分外完整的电路图

PFC强制SKIP待机

为了达到更高的效率,PFC部分使用了onsemi的图腾柱PFC NCP1680。NCP1680具有外部信号强制待机功能,当PIN2或PIN4脚加上一个超过50us宽的低电平脉冲后会让NCP1680进入强制SKIP模式,使得PFC的输出电压在94%-100%之间波动。

具体来说就是检测到强制待机信号后,输出关断,BULK电容下降,当下降到额定输出的94%后PFC开始工作,BULK电压又开始上升,当上升到额定输出后PFC又关断,往复循环直至强制待机信号消失,通过上述操作强制增大PFC的输出纹波电压来减少PFC的

开关时间以便获得更好的轻载效率,更详细的描述请参考NCP1680技术资料。

为了能让PFC能进入强制待机模式,设计了一个外加电路,根据NCP1345的SKIP模式下的驱动波形包络线产生对应的脉冲信号输入到PFC的PIN4脚SKIP脚,当PWM进入SKIP模式时就会让PFC也进入强制待机模式。电路图上R71,R95,D14,ZD5,C65,Q12组成这一电路。如果用其它PFC则可省略这部分电路。

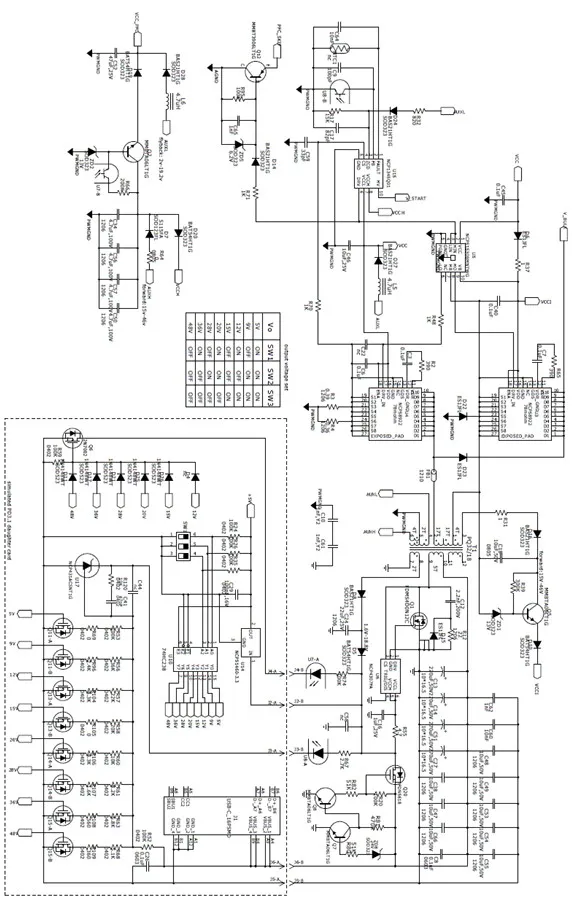

分立器件模拟PD0输出的PD卡

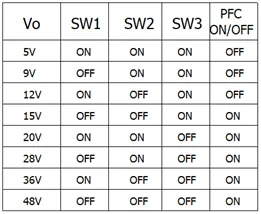

本方案设计之时还没有合适的48V PD协议控制器发布,为了更好的评估双管Flyback DC/DC部分的效率特地设计了一款仿真PD0输出的模拟子卡,它只能输出PD0电压不能输出AVS电压。这个子卡可以通过其上的三位DIP开关设置8个不同的输出电压,同时可以根据不同的输出电压值输出PFC ON/OFF信号通过

光耦来控制PFC的开关。

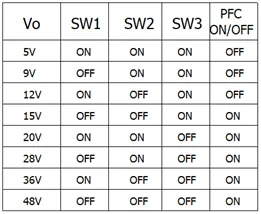

3位DIP开关的8个组合设定8个不同的输出电压,输出信号经3-8译码器后控制431的参考电压产生8个输出电压。同时对应输出的控制信号产生PFC ON/OFF给光耦控制PFC的VCC电压。DIP开关位置对应的输出电压及输出电压对应PFC ON/OFF状态如图7所示。

图7.3位DIP开关对应的PDO输出电压及PFC状态

仿真PD0输出控制电路带来的几个问题

1.双管反激变换器要求Vin_min>N*Vo, 所以当电源在90VAC开机后,在满载的情况下从5V转换到高压,比如48V,但PD子卡在输出电压变化的同时PFC ON信号发出开通PFC,在PFC输出电压上升缓慢,在BULK电压还没上升到N*48V时,输入电压是小于N*48V的,这时候反射电压被钳位,输出电压会下跌占空比增大峰值电流升高直至OLP过载保护,所以电源在低压输入时输出从低压(PFC处于OFF的输出电压)转高压是不成功的。

测试样板临时解决方案:设置输入电压整流后的电压高于N*Vo,那么从低压转高压时的Vin_min是大于N*Vo的,这样电压转换就能顺利进行不会触发保护。

终解决方案:PD协议控制器可以设置先送出PFC ON信号然后延迟一定的时间再转换输出参考电压,确保这个延迟时间大于PFC在90VAC和满载时BULK电压的上升时间即可,这样在BULK电压上升到额定值后才会转换输出电压,保证任何时候BULK电压大于N*Vo.

2.仿真PD卡和同步整流的供电电压由输出和输出辅助绕组电压在不同的输出电压下自动切换,这个切换点大约在输出25V左右。当输出电压切换跨过这个电压值时,比如从9V到28V切换,输出电压参考和反馈光耦的供电电压同时瞬变,环路根本无法调节两种电压的突变,所以会造成输出电压较大的过冲,输出电压变化只要不跨过这个值就不会有输出过冲。

终解决方案:PD协议控制器的参考电压变化都是一步步经过一定的时间才改变完成的,这个时间一般有数十毫秒,所以反馈环路有充足的时间来调整输出不会有任何过冲。

3.同步IC和反馈光耦的供电在28V输出时是由辅助绕组供电的,但输出辅助绕组电压在28V时时是电压,所以当输出在较大的负载下从9V切换28V或48V切换到28V时,由于仿真PD卡的输出参考是突变的,会造成反馈光耦供电电压跌落较大,低于正常工作电压造成反馈环路工作不正常,输出电压不能正常切换。

测试样板临时解决方案:可把输出负载设置空载或非常小的负载,那么电压切换时反馈光耦供电电压就不会跌落较多,电路就可以正常工作

终解决方案:PD协议控制器的输出电压参考缓慢逐渐变化使得反馈调整正常,这个电压就不会跌落较多而保持反馈环路正常工作。

结论:根据上面的分析,只要设计一款PD协议控制卡并且按上面的要求更改控制器的部分时序就能满足要求。协议控制器的电压参考转换一直就是逐步变化的,不需要特别修改。

方案中的其它几个关键器件选择

1.主开关管:使用了onsemi的内置驱动的GaN NCP58922,NCP58922是onsemi NCP5892X系列Drive GaN中的一种,DFN8*8封装,75mohm的内阻,可以提供5V参考输出,可通过输出极的RC供电网络设置开关速度,有使能控制端。在这个设计里也可以改用为150mohm的NCP58920来降低成本。

2.同步整流控制器:使用了onsemi的一代的同步整流控制器NCP4307,具有高低压两个VCC端子,可以分段供电,同时可以通过CS端子内部的LDO给VCC电容充电,35V的VCC范围。同步管可以高边也可以低边放置,高达7A/2A的Sink/Source电流,DCM/QR/CCM/Forward/ACF/LLC模式下都可工作,高达1MHZ的工作频率,CS端耐压200V。

3.同步MOS选FDMS4D0N12C,120V4.4mΩ的管子。

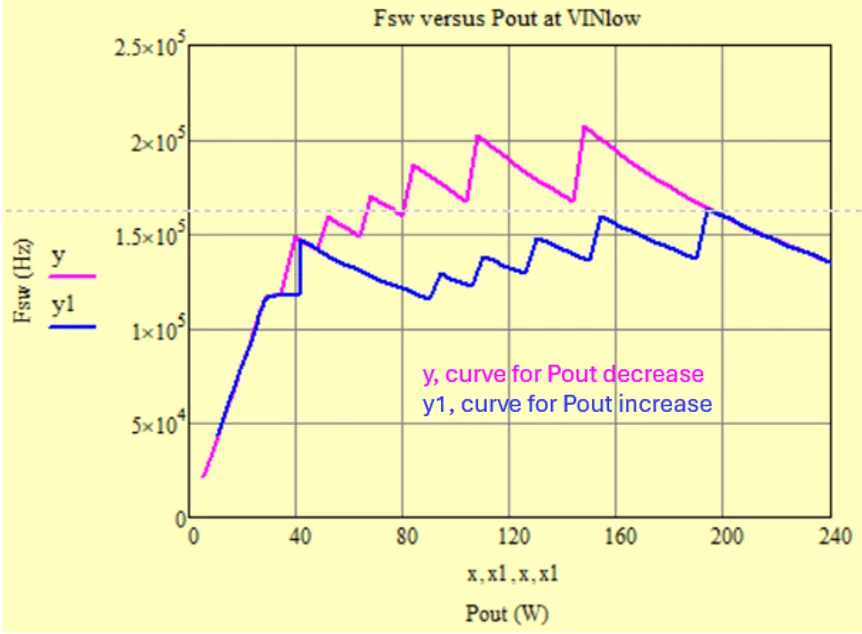

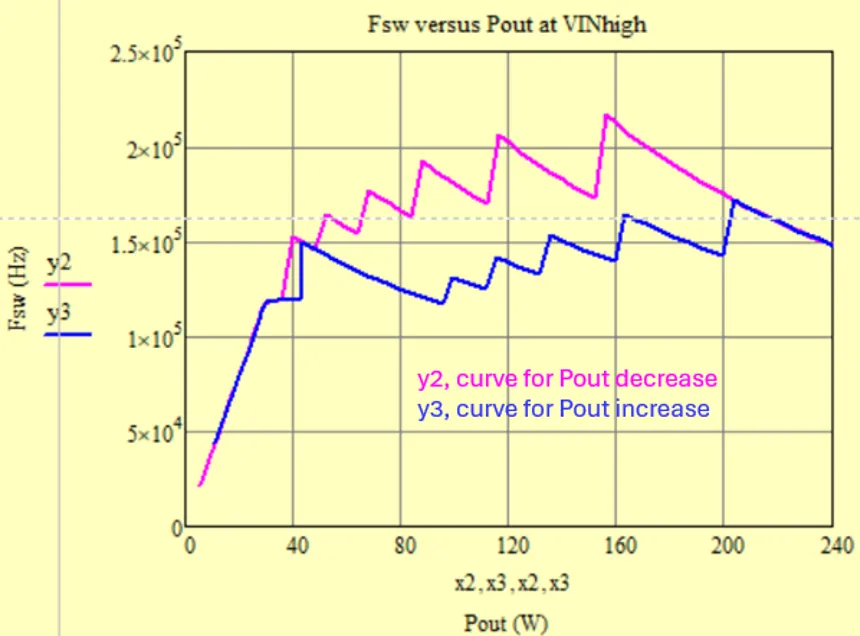

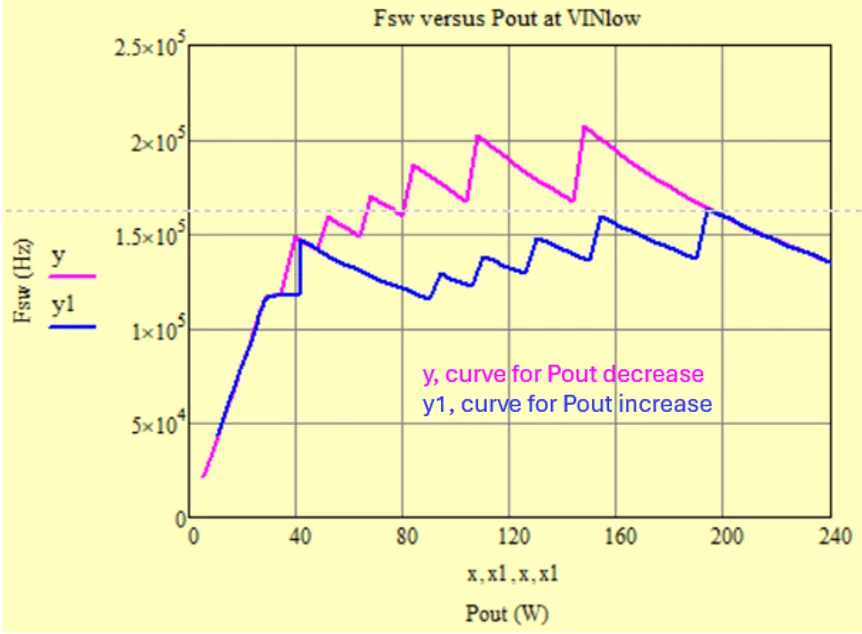

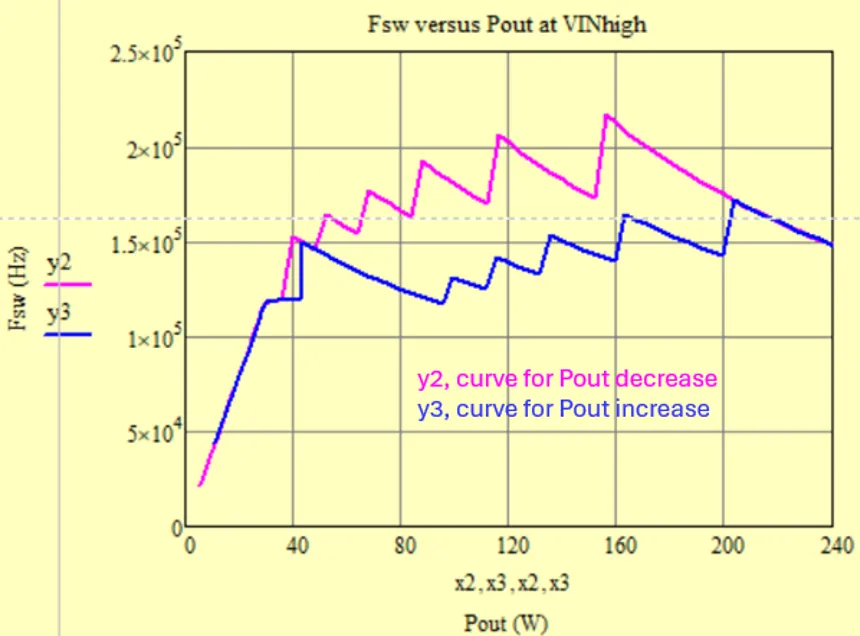

评估指定输入电压下的开关频率对负载曲线 根据频率计算公式,用MathCAD绘制的频率对输出功率的曲线如下图所示:

图7. 低压350VDC输入时的频率曲线

图8. 正常电压390VDC输入时的频率曲线

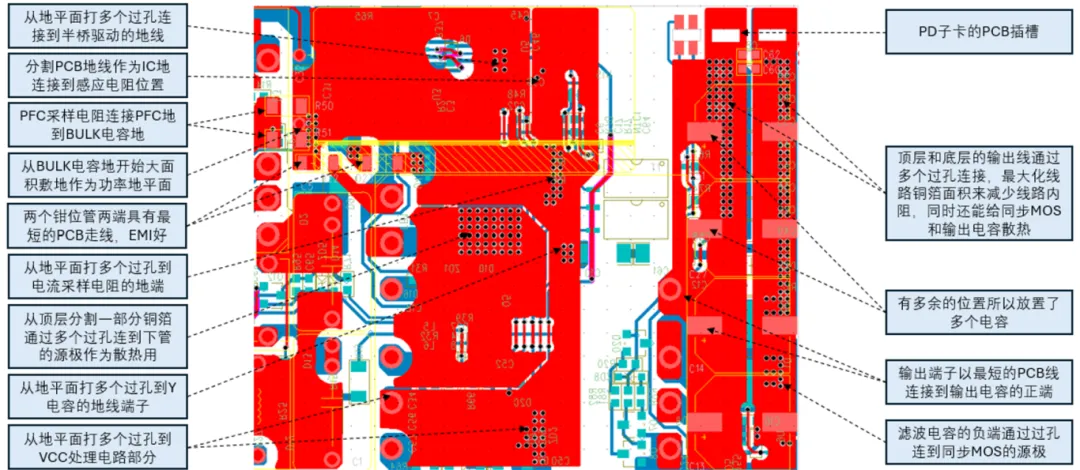

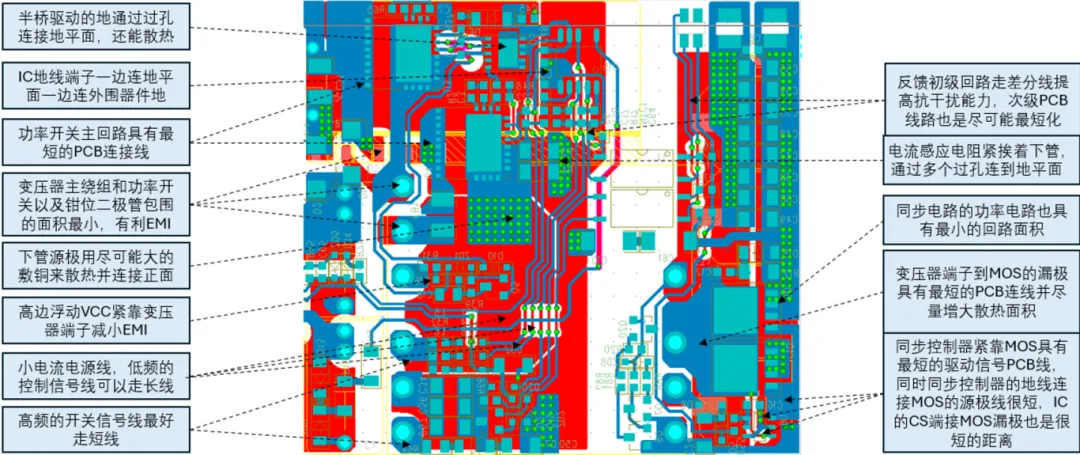

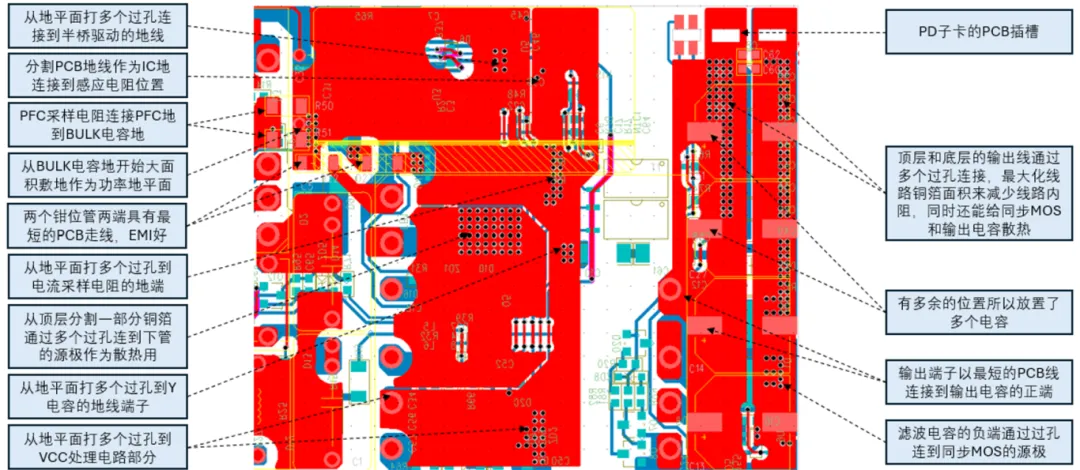

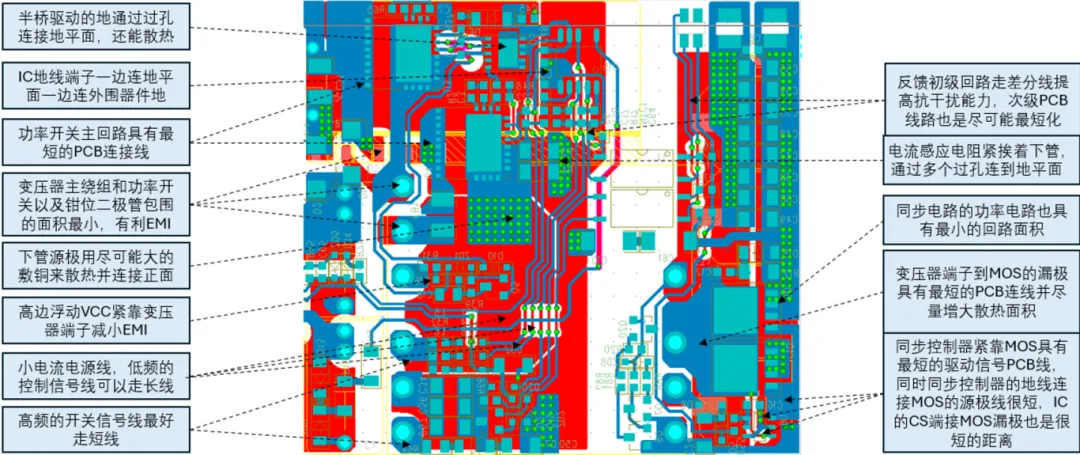

PCB Layout考虑 由于设计的的开关频率都有133KHz,在正常输入390VDC满载情况下频率接近150KHz,频率超过200KHz,所以想要电流稳定可靠的工作Layout变得相当重要。考虑到PCB的成本,参考设计采用了双层PCB,所以Layout中地线走线尤其重要,特别是PWM及后级同步整流部分的地线连接位置。 图9,图10显示PWM部分Layout顶层和底层的PCB线路图,并详细描述了各部分的一些走线规则及带来的好处。实际应用中每个设计的布局布线不可能完全相同,但有些规则是相同的,可能的情况下尽量满足。

设计调试注意事项

1.空载Vcc是否足够,因为考虑到损耗问题,所以初级的三个辅助Vcc绕组电压大小设计的都比较临界,在空载深度SKIP状态下纹波比较大,所以滤波电容要足够大才能小纹波维持足够的Vcc电压。必要情况下可以部分用肖特基

二极管代替超快恢复管来提升Vcc电压。

2.由于GaN的电压只有20V,所以auxl绕组电压上限有点临界,两路auxl绕组整流后给NCP1345 Vccl和PFC电路供电的整流回路都加了电感来抑制漏感产生的高电压,确保这两个电压不超过20V。

3.目前通过ZCD脚设置的OVP值比较高约57V左右,原因是现在用的仿真PD卡在电压切换时有较高的电压过冲,防止触发OVP所以设置的比较高。未来用了PD控制器就不会有过冲电压,可以降低OVP的保护值,参考前面介绍。

4.整机的工作频率比较高,所以在高频功率回路上用的二极管都是超快恢复二级管,25nS恢复时间,比如ES1JFA。高频小信号回路及部分小电流Vcc整流都是用高速

开关二极管比如BAS21等。

5.控制PFC强制SKIP的电路在调试时要注意驱动信号整流滤波后的相位不能延迟太多,幅度要确保Q12既能开通又能截止,如果相位幅度偏差较大,可调整R71,C65,ZD5的值。

6.L6,D28是额外整流Vccl绕组给PFC供电的,在28V及以上输出时PFC肯定是工作的,但如果由Q2稳压来供电损耗比较大,而28V以上输出时auxl整流后的电压超过10V足够PFC工作,所以才用auxl绕组来供电,如果觉得麻烦也可拿到这个整流电路。

7.Auxh绕组整流后一边通过稳压及次级PFC控制后供电PFC,一边通过D20给NCP1345的Vcch供电,D20可以拿掉来提高空载时供给Vcch的电压。

8.GaN的11,12脚的RC网络可以调节GaN内部驱动的Vdd上升速度,因为低边的驱动是通过NCP51530的所以NCP1345的自适应驱动来降低次级应力功能失效,所以只能通过调节下管这个RC网络的电阻来降低次级应力。可以看出上下管的这个R的阻值不同,原因如此。

9.如果不是开通在谷底的点,请调整C17的容量大小。开通点在谷底偏后(Vds波形在谷底后上翘后才开通)就增大容量,如果偏前一点(没到谷底)就减小容量使正好谷底开通。

10.由于输出电压变化范围很大,所以有时候反馈环路在48V是稳定的,但在5V会有自激现象,遇到这种情况一般只要调整增大反馈光耦1脚上的电阻减少环路增益即可解决。

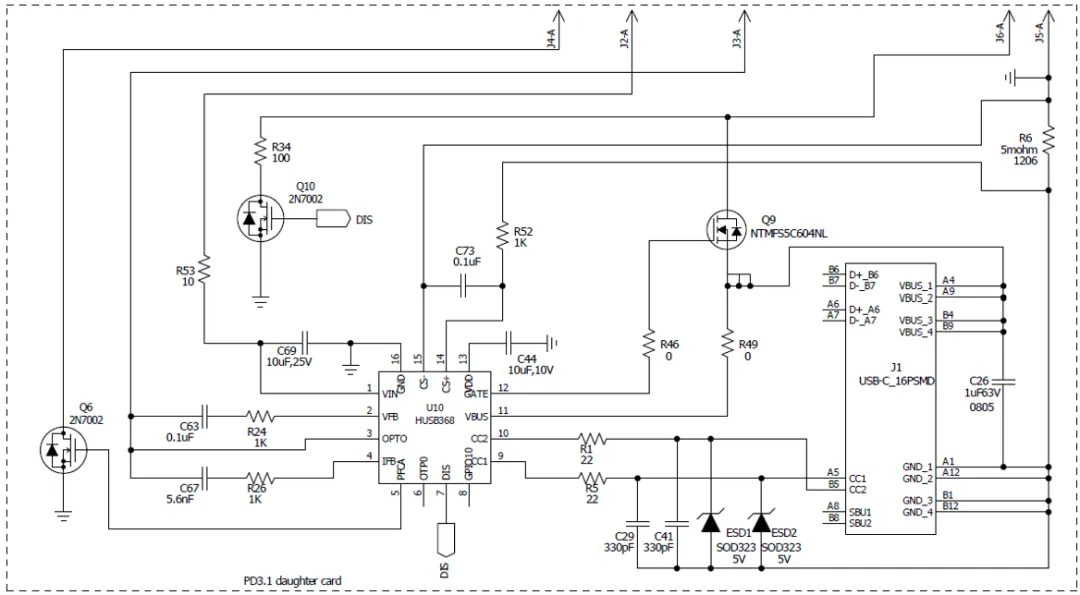

附慧能泰48V PD协议控制器配合本方案的PD子卡电路图如图11所示。

图9. PWM部分顶层Layout图及走线规则特

图10. PWM部分底层Layout图及走线规则特点

图11. HUSB368 PD3.1子卡电路图

结论

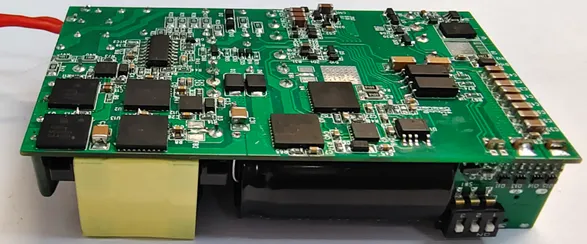

本文详细介绍了用高频QR控制器NCP1345来设计双管反激变换器240W PD3.1 EPR参考设计的整个流程,包括BULK纹波电压值的计算,匝比的条件约束,变压器的参数及IC外围主要端子的功能参数设计等。参考该设计流程也能容易地设计140W, 180W的PD EPR方案。给出了详细的240W方案的原理图,并介绍了关键的功能设计,给出了Layout的实例并详细介绍了关键电路的Layout要求,也给出了设计调试过程中需要注意的问题。

有关QR Flyback的计算,也可MathCAD计算工具来进行,后台回复“工具”,即可。

由于本设计进行之时没有合适的48V PD控制器发布,所以用分立器件来模拟部分PD功能,旨在测试DC/DC部分的关键效率指标,在有限空间的PCB子卡上不能完善所有要求的功能,这会给DEMO板的正常测试带来一些问题,文中也给出了应急的测试方法。

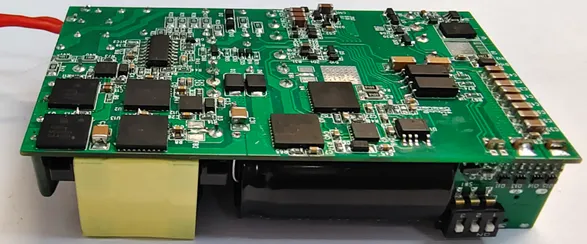

附上用慧能泰48V PD3.1协议控制器所做的PD子卡的原理图,接口界面完全匹配原始的仿真PD卡接口。 如果想要详细了解该参考设计的性能,请登陆www.onsemi.com阅读该参考设计的样板手册。图12是该参考设计样板的照片。

图12. 240W PD3.1 EPR参考设计样板实物照片

图10. PWM部分底层Layout图及走线规则特点

图10. PWM部分底层Layout图及走线规则特点