D 型触发器是基本的数字存储元件。在这里,我们检查它们的输入输出行为和内部电路。

逻辑门是所有数字技术的构建模块。然而,现代世界的大量计算功能仅靠组合逻辑 电路是不可能实现的。在完全由组合逻辑组成的电路中,输出仅取决于输入的当前状态。所有信号通过互连的逻辑门直接从输入传输到输出。

为了实现与当今数字技术相关的计算和信号处理,我们需要组合逻辑和数字

存储器。换句话说,我们需要顺序逻辑。虽然组合逻辑使我们能够构建有用的设备,例如加法器、多路复用器和编码器,但顺序逻辑使我们能够进入

微处理器领域。

在时序

逻辑电路中,输出取决于输入信号的序列(当前状态和历史状态)。这允许创建带有存储器的数字设备,例如锁存器和触发器。然而,尽管这两种电路类型都用作数字存储设备,但它们之间存在重要区别:

锁存器是电平触发的,这意味着当“使能”输入处于活动状态时(例如,在时钟信号的逻辑高脉冲期间),它会对输入信号做出响应。

触发器是边沿触发的,这意味着当“使能”输入改变状态时(例如,在时钟信号的上升沿),它会对输入信号做出响应。

在实际应用中,通常更希望有一个仅在特定事件发生时对输入状态敏感的存储设备。因此,人字拖的使用更加广泛。

在我看来,D 触发器是重要的触发器,我什至称其为重要的数字存储器子电路。在本文中,我们将了解其电气行为和内部结构。

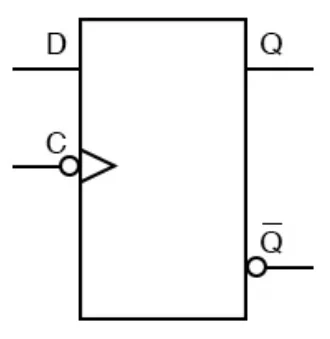

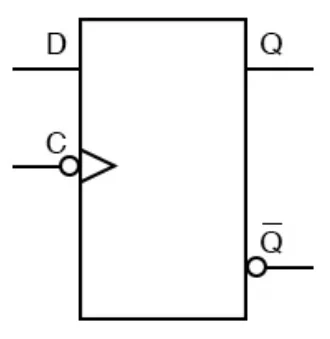

什么是 D 触发器? D 触发器因其单一数据输入而得名,它的功能正是存储单元需要执行的功能 - 它在控制信号有效转换时将输入逻辑电平存储为输出电压,而在所有其他时间都简单地执行保留输出电压。

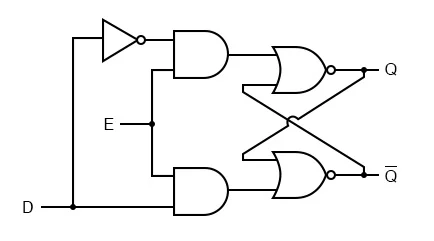

图 1 显示了一个基本的 D 触发器。如您所见,它有四个终端:

数据输入 ( D )。

时钟或控制输入 ( C )。

输出 ( Q )。

输出的反转版本 ( Q? )。

基本 D 触发器的电路符号。

图 1.基本 D 触发器的电路符号。这些

端子是数据输入 ( D )、时钟或控制输入 ( C )、输出 ( Q ) 和输出的反相版本 ( Q )。图片由Tony R. Kuphaldt提供 表 1 描述了响应时钟信号上升沿的 D 触发器的操作。

问

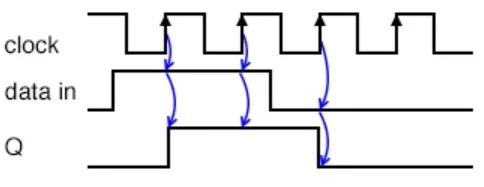

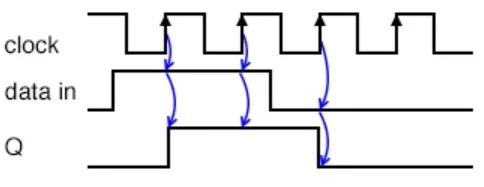

下降沿行中的 X 表示D的逻辑电平不相关。Q仅受上升沿输入状态的影响。在时钟信号的上升沿,数据输入被采样并传递到Q输出。通过查看图 2 中的时序图,我们可以在时域中看到这一点。 D 触发器的时序图。

图 2.D触发器的时序图。图片(已修改)由Tony R. Kuphaldt提供

由同一时钟信号的上升沿或下降沿控制的八个D触发器可以充当一字节(8位)寄存器。当与解码电路结合时,一组单字节寄存器充当存储体。

为了了解 D 触发器的内部逻辑门结构,让我们检查以下功能块:

SR锁存器。

D锁存器。

脉冲检测器。

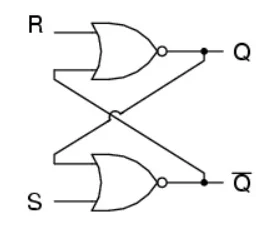

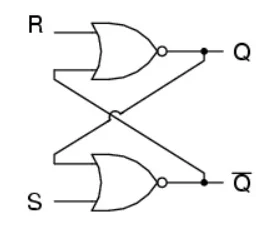

SR 锁存器 设置-复位 (SR) 锁存器是时序逻辑的基础子电路。该锁存器通过反馈实现记忆,可以由或非门或与非门构建。图 3 显示了作为两个交叉耦合 NOR 门实现的 SR 锁存器。

SR 锁存器使用两个或非门实现。

图 3. SR 锁存器实现为两个交叉耦合的 NOR 门。图片由Tony R. Kuphaldt提供

将输出信号反馈回输入端子允许 SR 锁存器保留先前的输出状态。下面的真值表指定了锁存器的输入输出行为。

表 2. SR 锁存器真值表。

无效的

要了解此行为,请考虑以下事件序列:

首先,我们假设S为高,R为低。因此Q值会很高。

现在将S驱动至逻辑低电平。现在两个输入都很低,而Q仍然很高——它是“锁定的”,这意味着它保留了之前的状态。

现在将R驱动至逻辑高电平。当R为逻辑高电平、S为逻辑低电平时,Q将为低电平。

现在将R驱动至逻辑低电平。再次,两个输入都为低电平,但这次Q为低电平。

相同的输入组合在步骤 4 中产生与步骤 2 不同的输出状态。这是因为电路同时受到当前输入状态和先前输出状态的影响。

为了使 SR 锁存器更有用,我们需要额外的电路来确定锁存器何时响应或不响应其输入状态。图 4 显示了“门控”SR 锁存器,即具有启用/禁用信号的 SR 锁存器。控制信号标记为E,表示“启用”。 门控 SR 锁存器。

图 4.门控 SR 锁存器。图片由Tony R. Kuphaldt提供

通过这一添加,我们现在有了一个电平触发的锁存器——当E为低电平时,锁存器的作用就像S和R为低电平一样。换句话说,E上的逻辑低电平会将锁存器置于保留先前输出模式,而不管S和R输入的真实状态如何。

D 锁存器

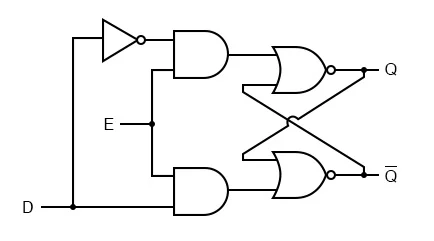

从技术上讲,我们不需要同时设置和重置输入来存储单个内存位。仅存储一个输入信号的逻辑电平的存储单元更直观。这就是我们使用 D 锁存器的原因(图 5)。

AD锁存器。

图 5. AD 锁存器。图片由Tony R. Kuphaldt提供

如图所示,D 锁存器只是一个门控 SR 锁存器,其中S输入被重命名为D,而R输入始终是D的反相。这种安排使得S = R = 1(无效)状态和S = R = 0(锁存)状态不可能。正如我们在表 3 中看到的,Q跟随D,并且锁存模式仅通过E信号来实现。

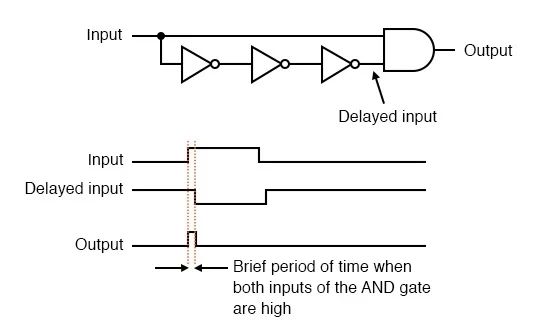

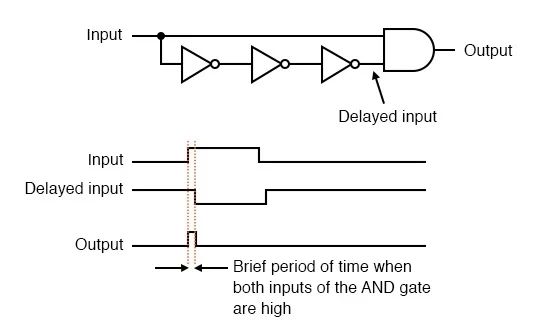

脉冲检测器

要将电平触发的 D 锁存器转变为边沿触发的 D 触发器,我们需要一个脉冲检测器,该电路将宽脉冲转换为与脉冲的上升沿或下降沿对齐的非常窄的脉冲。图 6 中的图表描述了实现脉冲检测器的一种方法。在这里,多个串联连接的

逆变器会产生短暂的延迟。与门使用主输入和延迟输入来创建窄脉冲。 使用多个串联逆变器构建的脉冲检测器。

图 6.使用多个串联逆变器构建的脉冲检测器。图片由Tony R. Kuphaldt提供

如果我们将 D 锁存器的E信号通过脉冲检测器,然后将其馈送到与门,我们将得到一个 D 触发器,它的作用就好像它仅在E信号的上升沿或下降沿时响应输入一样。实际上,触发器仍然是电平触发的,但现在感兴趣的电平是脉冲检测器输出的活动状态。这种活跃状态总是非常短暂。

无效的

无效的