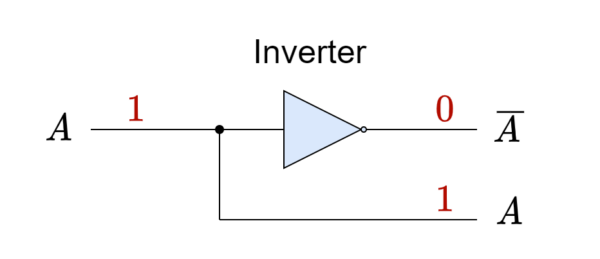

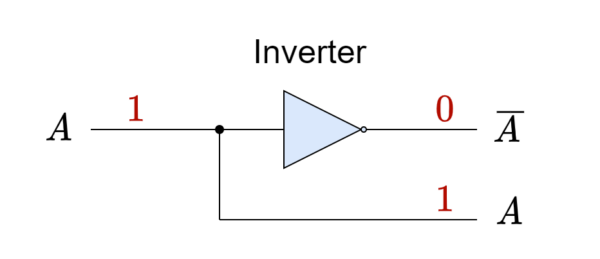

二进制解码器是执行编码器逆过程的组合逻辑电路。它通过解码从编码器的编码输出信号产生原始二进制输入数据或信号。“解码器”术语定义了一种将信息从一种格式转换为另一种格式的设备,更具体地说,它使用 2 n 个输出将“n”个二进制输入信号转换为等效代码。它与之前的优先级编码器文章中讨论的编码器完全相反。二进制解码器是一种数字逻辑器件,根据输入线的数量,可以输入2位、3位或4位的二进制代码。一般来说,解码器可以说具有 n 位代码,并且可以将这个 n 位代码表示为等效的 2 n 个可能值。“二进制解码器”可以通过将 2 n 个输出之一设置为逻辑“1”来解码该 n 位代码。“逆变器”可以称为 1 对 2 二进制解码器,如下图所示。当的输入为逻辑“0”时,个输出设置为逻辑“1”,对于逻辑“1”输入,第二个输出变为“高”。因此,在任何情况下,根据输入数据,只有一个输出为“高”。二进制解码器通常将编码信号转换为另一个不同的编码信号。编码输入信号可以是二进制或二进制编码十进制 (BCD),使用二进制解码器将其转换为十进制代码。与输入 (n) 线相比,二进制解码器具有更多的输出线 (2 n ),并采用 2 至 4、3 至 8 和 4 至 16 的配置。市售 BCD 至十进制解码器包括 CMOS 4028 和 TTL 7442 IC 封装。

逆变器图 1:作为 1 对 2 二进制解码器的逆变器

在标准化形式中,它是一个 n 到 m 的解码器,并且 m 小于或等于 2 n。简而言之,二进制解码器通过查看输入线上存在的二进制代码或数字来决定将哪条输出线设置为“高”。

2 至 4 个二进制解码器 2 至 4 二进制解码器,顾名思义,有两个输入和四个输出。下图中,显示了一个 2 至 4 二进制解码器,它包含四个与门和两个反相器的阵列及其框图和真值表。从真值表中可以明显看出,根据输入,其中一个输出将被设置为“高”。例如,当两个输入均为“低”时,则输出 (Q 0 ) 将设置为“高”。因此,输出之一的“高”状态将指示输入的状态或输入处存在的二进制代码,并且可以说是“解码”输入。

2 至 4 线二进制解码器图 2:使用与门及其真值表的 2 至 4 行二进制解码器 在微处理器

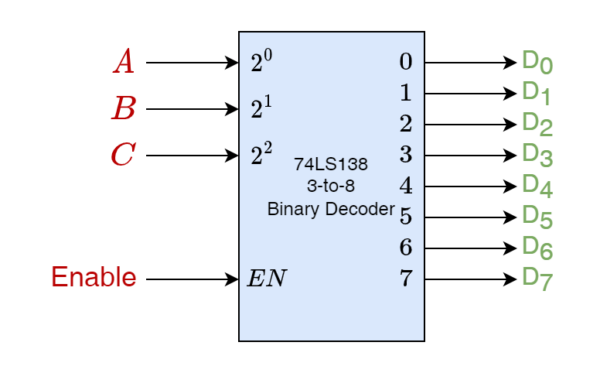

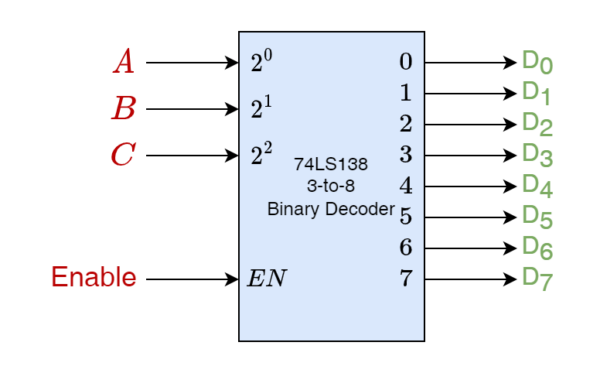

存储器应用中,二进制解码器具有额外的“启用”输入,可以根据存储器地址选择的要求打开或关闭解码过程。用于此目的的解码器称为“存储器地址解码器”。商用 2 至 4 二进制解码器的一个示例是 TTL 74155。在较大或复杂的数字系统中,需要高阶二进制解码器,并且可以使用 2 n确定输入和输出的数量。因此,对于三 (3) 个二进制输入,总输出为 2 3 = 8,并呈现一个 3 至 8 二进制解码器。

3 至 8 线二进制解码器模块图 3:具有使能引脚的 3 至 8 线二进制解码器的框图

同样,四 (4) 个输入将产生一个 4 至 16 二进制解码器 (2 4 = 16)。市售的3转8和4转16二进制解码器分别是TTL 74138和TTL 74154。二进制解码器可以具有等于或小于由 2 n给出的二进制输出。例如,BCD(二进制编码十进制)到 7 段

转换器具有四 (4) 个输入,而总共 2 4 = 16 个输出中只有七 (7) 个输出。BCD 至 7 段解码器以 TTL 7447 封装形式在市场上销售。

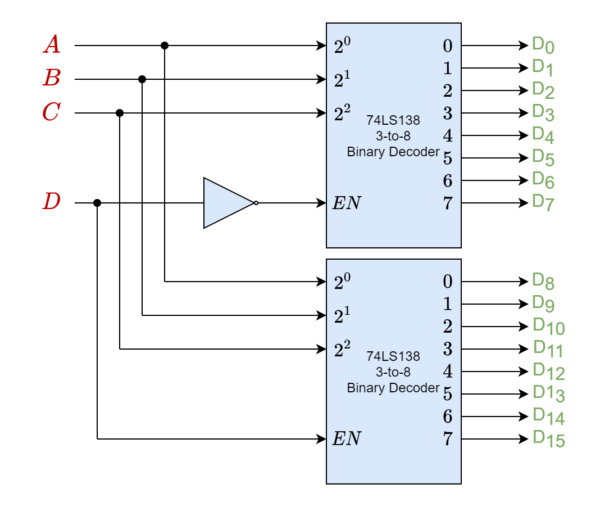

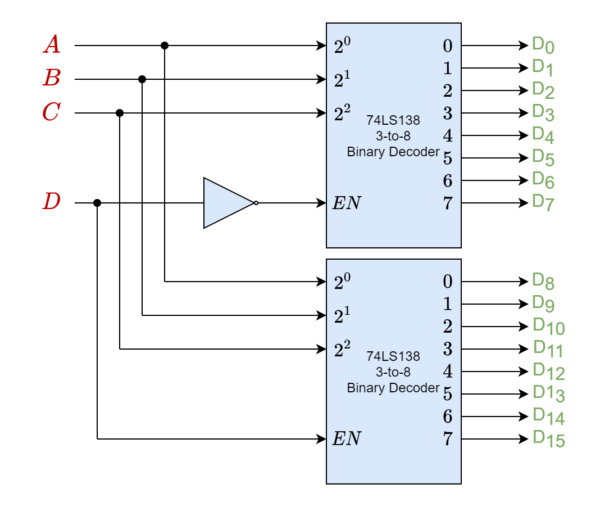

4 至 16 个二进制解码器 上面所示的 3 至 8 二进制解码器用于在附加输入“启用”的帮助下实现 4 至 8 变体。4 至 16 二进制解码器的配置如下图所示。

图 4:4 至 16 线二进制解码器的框图

每个 3 至 8 二进制解码器均按照上述方式工作,除了第四个输入 (D) 启用两个 3 至 8 二进制解码器中的任意一个。由此构成一个4至16位二进制解码器。这种配置涉及解码器可以容纳的输入(与门)的数量,而不会导致门的扇出导致它们变大。二进制解码器通常使用 AND 加 NOT 门或仅使用 NAND 门来构建。当输入之一为“高”时,二进制解码器的与门配置会产生“高”输出。另一方面,当其中一个输入为“高”时,NAND 配置在相应输出处产生“低”。与非门配置的生产成本较低,因为它需要更少的

晶体管来实现。

2 至 4 线 NAND 二进制解码器

如上所述,基于与门的二进制解码器在其输出之一上给出逻辑“高”,而基于与非门的二进制解码器在其输出之一上给出逻辑“低”,而所有其他输出被设置为“高”逻辑状态。下图所示为使用 NAND 门的 2 至 4 二进制解码器。

2 至 4 线二进制解码器图 5:使用“与”门的 2 至 4 行二进制解码器及其真值表

除了两个二进制输入之外,第三个输入“启用”用于通过分别将其设置为“低”和“高”状态来“关闭”和“打开”解码功能。在 NAND 门配置中,Enable = 0 将输出设置为逻辑“低”或“0”,无论输入状态如何。

内存地址解码器

二进制解码器重要的应用是在选择或解码特定存储器地址的存储器系统中。这种应用在较大或复杂的存储器系统中更为深刻,其中多个存储器芯片通过单个数据总线连接到微处理器。使用地址解码技术单独选择一个存储芯片。存储芯片的特定地址由编码数据输入表示,输出选择与该地址相关的特定存储芯片。内存芯片或存储设备具有“片选”或“CS”,当设置为“高”时会调用它们。内存解码器的输出连接到所有内存芯片的“CS”输入。编码输入或存储器地址通过连接到特定存储器芯片的“CS”引脚的特定输出线来选择或取消选择相关存储器芯片。通常,在输出线上,逻辑“高”选择特定存储器芯片,逻辑“低”取消选择特定存储器芯片。使用这种内存解码技术,2 至 4 内存解码器可用于仅使用两 (2) 个二进制输入来选择四 (4) 个内存芯片。

内存地址解码示例 考虑到每个内存位置包含一个字节(8 位)数据,总共有 128 个这样的位置。这构成了具有 (128 X 8) = 1024 位或 1 Kb 存储容量的单个存储芯片。该单个存储器芯片需要八 (8) 位数据总线,用于从每个存储器位置读取 8 位(1 字节),以及七 (7) 位地址线,用于表示从 0 到 127 (2 7= 128) 内存地址。现在,通过使用 3 到 8 个内存解码器,内存容量可以增加到 8 X 1 kb = 8 Kb,并且可以管理八 (8) 个这样的内存芯片的堆栈。使用“CS”引脚选择特定的存储器芯片,该引脚通过 3 至 8 存储器解码器驱动,然后 7 位地址线在该特定存储器芯片的 128 个地址中选择特定的存储器地址。使用下图对此进行说明。 内存地址解码图 6:使用二进制 3 至 8 解码器的存储器寻址和选择示例

上图中,微处理器单元(MPU)生成一个10位内存地址,该地址由低位和高位两部分组成。下部由三 (3) 位组成,用于选择特定的存储芯片,而上部由七 (7) 位组成,用于从 128 个位置中选择特定的存储位置。较低部分(3 位)被编码输入到 3 至 8 存储器解码器,该解码器选择 1 Kb 的特定存储器芯片。例如,如果MPU发出地址“0110000101”,则低位部分(3个LSB位)即“101”选择第5个存储芯片,而高位部分“0110000”则指向第49个存储位置作为存储位置从 0 开始,因此第 48个位置表示第 49 个内存位置。

结论

二进制解码器是一个组合逻辑电路,它将 n 位二进制编码数据解码为 2 n 个二进制输出。它执行二进制编码器的逆过程。二进制解码器的输入和输出配置为 2 至 4、3 至 8、4 至 16 等。对于 n 位二进制输入,二进制解码器有 2 n 个二进制输出。二进制解码器是使用 AND 或 NAND 逻辑门构建的。AND 结构在所选输出处输出“高”逻辑,而在 NAND 结构的情况下输出“低”逻辑。NAND 组合的构建成本较低,因为它使用的晶体管较少。二进制解码器主要用于复杂/大型数字系统的内存地址解码。使用二进制解码器,多个存储芯片通过“片选”输入引脚连接到一条数据总线。商业二进制解码器采用 2 至 4 (TTL 74154)、3 至 8 (TTL 74138) 和 4 至 16 (TTL 74155) IC 封装。