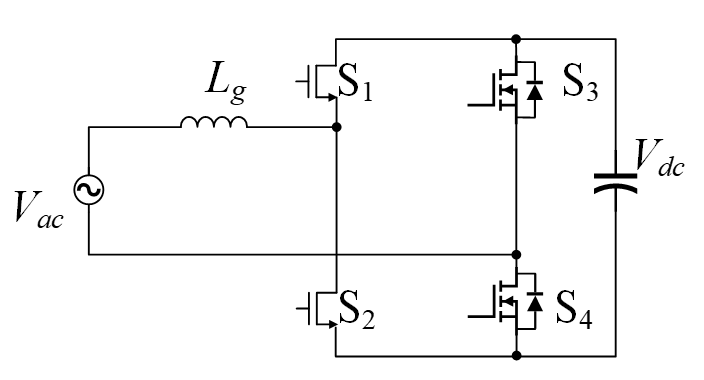

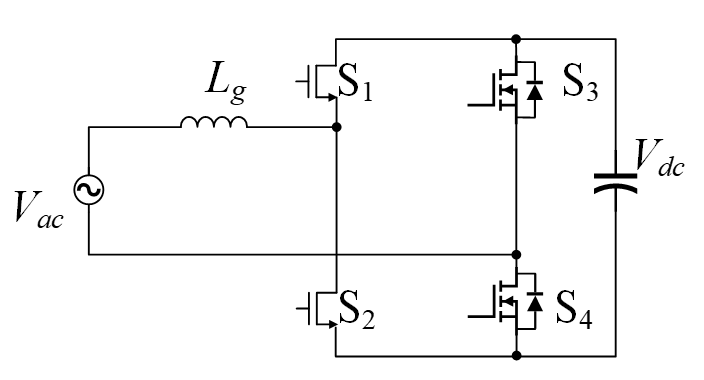

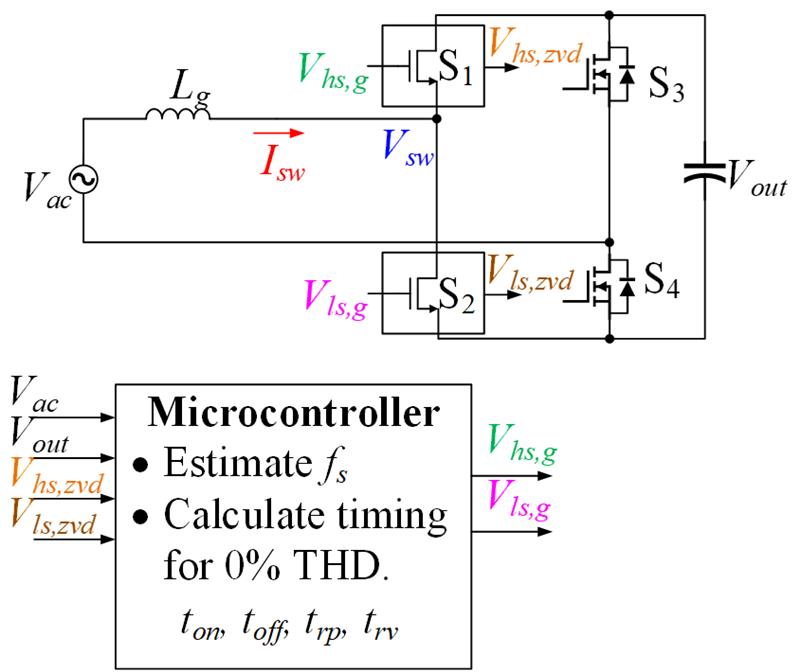

在本文中,我将研究服务器 5 kW 功率因数校正器 (PFC) 内使用的控制方法。该设计使用高性能 GaN FET 以的实用频率运行电源。该电源还采用了一种新颖的控制技术,可以从 GaN FET 中提取更多性能。终结果是具有更高功率密度的高效率、小尺寸设计。 FerriSSD 提供医疗设备所需的稳定性和数据安全性FerriSSD 提供医疗设备所需的稳定性和数据安全性2024年3月18日 边缘计算的量子飞跃:研华HPEC解决方案加速边缘演进边缘计算的量子飞跃:研华HPEC解决方案加速边缘演进2024年3月18日 众所周知,图腾柱 PFC 是高功率、高效率 PFC 的主力。图 1说明了该拓扑。

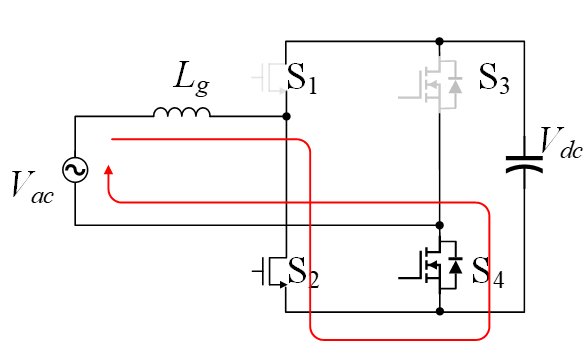

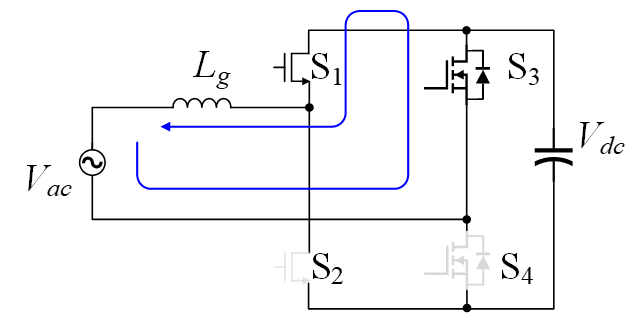

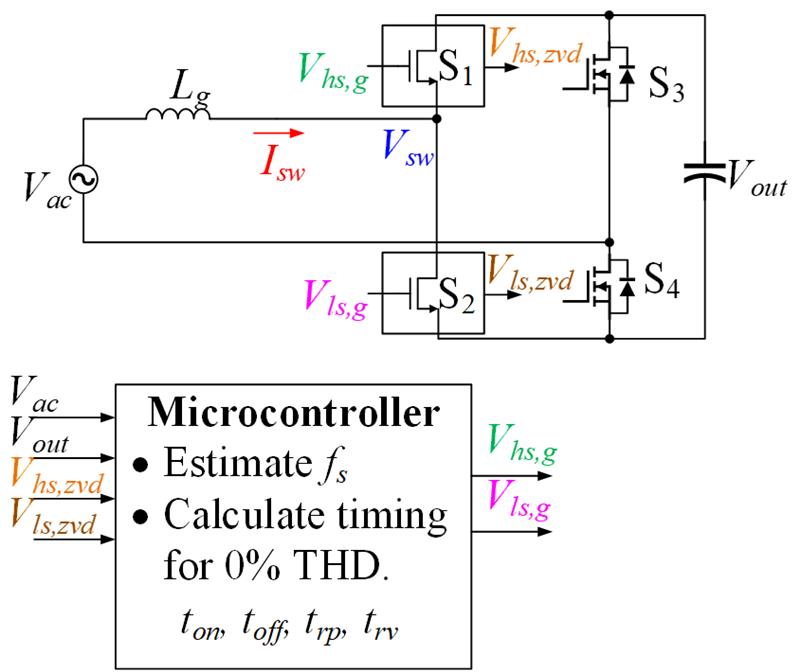

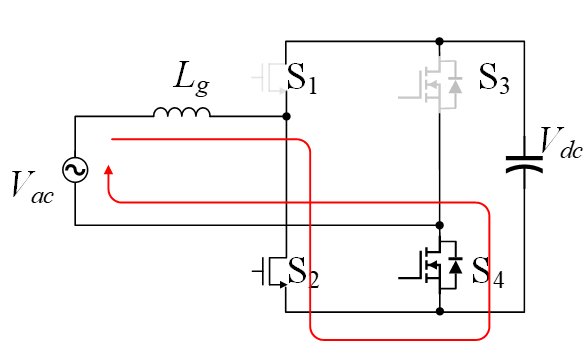

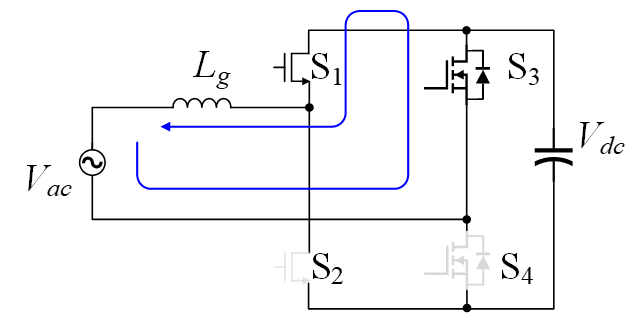

图 1基本图腾柱 PFC 拓扑,其中 S 1和 S 2是高频 GaN 开关,S 3和 S 4是低频开关 Si MOSFET。资料德州仪器S 1和S 2是高频GaN 开关,工作频率在70 kHz 到1.2 MHz 之间。S 3和S 4是在线路频率(50 至60 Hz)下工作的低频开关硅MOSFET。 在交流线路的正半周期期间,S 2用作控制 FET,S 1用作同步整流器。S 4始终开启,S 3始终关闭。图 2显示了由于控制 FET S 2导通而导致电感器电流增加的时间间隔。图3显示了电感电流通过同步整流器S 1放电的时间间隔。

图 2正半周期电感电流充电间隔。资料德州仪器

图 3正半周期电感放电间隔。资料德州仪器图 4和图 5显示了负半周期的相同行为。

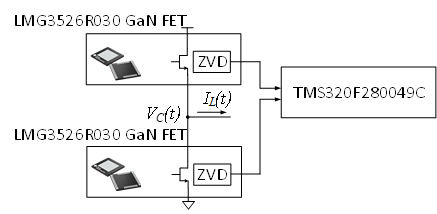

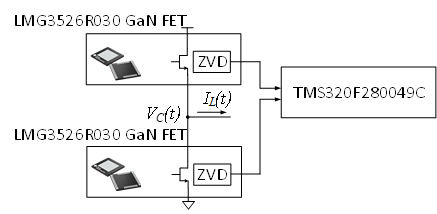

图 4负半周期电感电流充电间隔。资料德州仪器图 5负半周期电感放电间隔。资料德州仪器零电压开关 S 1和 S 2使用 GaN 开关,使转换器能够以更高的开关频率运行,同时开关的开通和关断损耗更低。然而,如果 GaN 开关可以通过零电压开关 (ZVS) 开启,则可以实现更高的频率。此设计的目标是在所有线路和负载条件下的每个开关周期实现 ZVS。为了做到这一点,你需要做两件事: 用于告知控制器是否已实现 ZVS 的反馈 微控制器可以实时执行的算法,以实现低总谐波失真 (THD)您可以通过 GaN 开关内部的集成零电压检测 (ZVD) 传感器来完成项任务 [1]。如果开关通过 ZVS 导通,ZVD 标志的工作方式是断言高电平信号;如果在导通时未实现 ZVS,则 ZVD 信号保持低电平。图 6和图 7说明了这种行为。

图 6采用具有集成驱动器、保护和温度功能的 LMG3425R030 GaN FET 以及 TMS320F280049C MCU 的 ZVD 反馈框图。资料德州仪器图 7带 ZVS 的 ZVD 信号(左)和不带 ZVS 的 ZVD 信号(右)。集成的 ZVD 传感器启用 ZVD 标志,如果开关通过 ZVS 打开,则可以看到该标志。

GaN 开关内可提供许多优势:少的组件数量、低延迟以及可靠的 ZVS 事件检测。

除了 ZVD 信号之外,您还需要一种能够计算开关时序参数的算法,以便同时实现 ZVS 和低 THD。图 8是实现该算法所需的硬件框图。

图 8基于 ZVD 的控制方法所需的硬件,该方法使算法能够计算开关时序参数,以同时实现 ZVS 和低 THD。资料德州仪器求解 GaN FET 漏源电压 (V DS ) 谐振跃迁的 ZVS 状态平面将为您提供此设计的算法。图 9显示了 GaN FET V DS、电感器电流和控制信号,以及时域图和状态平面图。

图 9具有 GaN FET V DS、电感器电流和控制信号的谐振过渡状态平面解决方案,以及时域图和状态平面图。资料德州仪器在图 9 的状态平面图中: “j”是每个死区时间间隔开始和结束时的归一化电流“m”是标准化电压 “θ”用于归一化时序参数 该图还显示了标准化关系。图 8 中的微控制器求解图 9 中所示的状态平面系统方程,以便系统实现 ZVS 和理想功率因数。ZVD 信号提供反馈,指示微控制器如何调整开关频率以满足 ZVS。

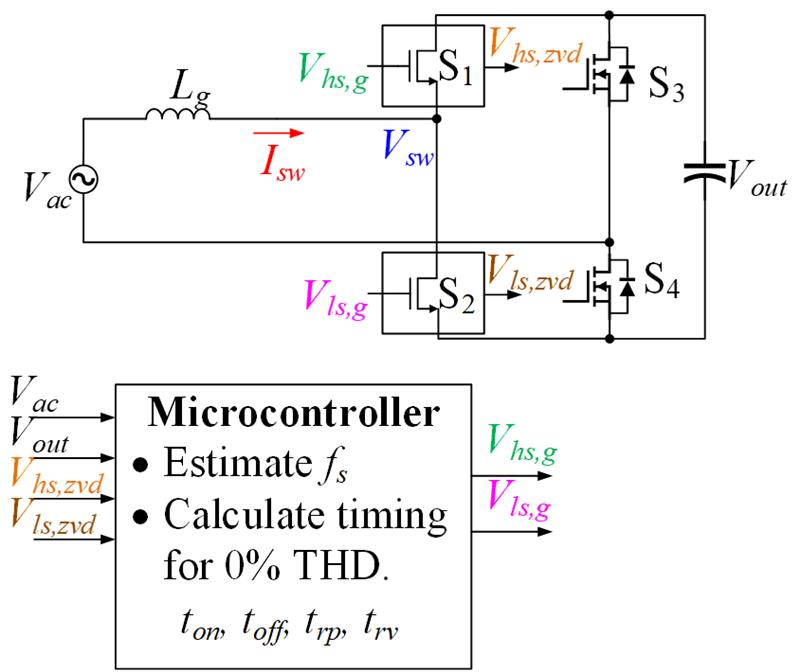

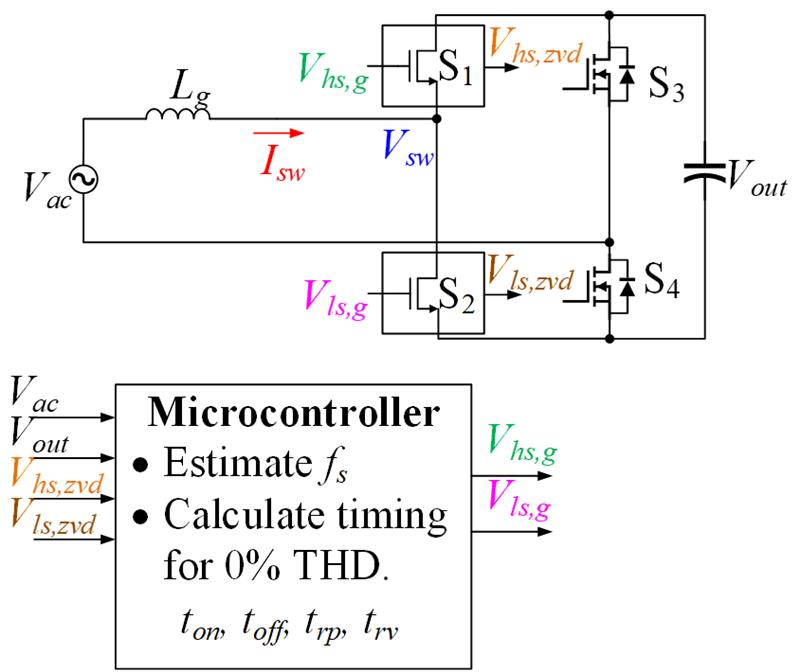

图 10显示了应用频率太低(左)、理想(中)和太高(右)时的工作波形。您可以看到,仅当应用频率处于理想值时,两个 ZVD 信号才会出现;因此,改变频率直到两个 FET 实现 ZVD 将揭示理想的工作点。 图 10应用频率太低(左)、理想(中)和太高(右)时的 ZVD 控制波形。资料德州仪器硬件性能 图 11是使用 GaN 和之前描述的算法的两相 5 kW 设计示例的照片。

图 11两相 5 kW 基于 GaN 的 PFC,具有应用算法所需的硬件,以实现更高的频率并提高整体解决方案的效率。资料德州仪器表 1列出了设计示例的规格。

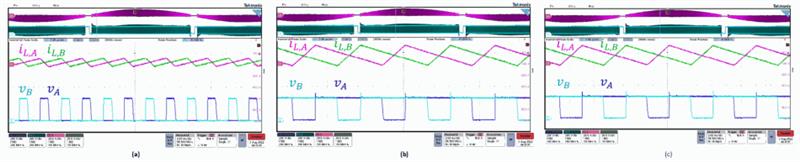

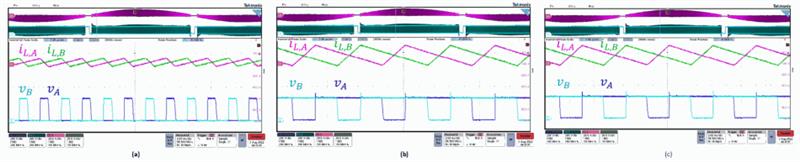

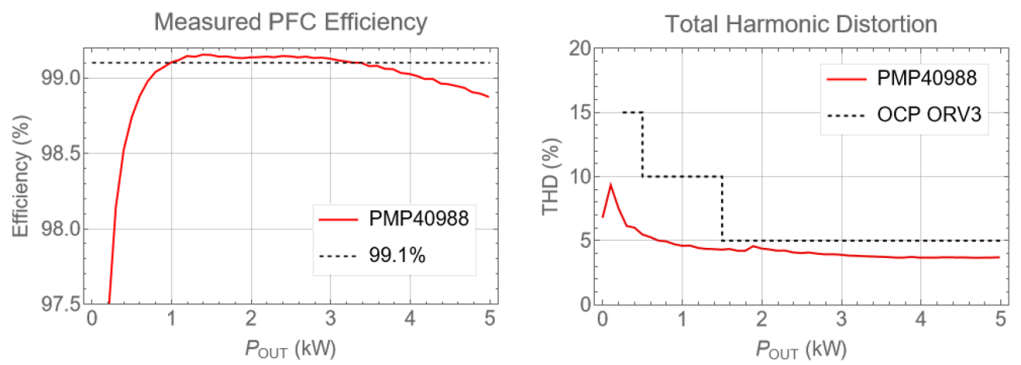

图 12显示了两相的电感器电流波形(I LA和 I LB)和 GaN FET V DS波形(V A和 V B)。这些图处于全功率状态,说明了三种不同的操作条件。在每种情况下,您都可以看到 ZVS 和正弦电流包络。所有三个图的条件均为 V IN = 230V RMS、V OUT = 400V、P = 5kW 以及 200V/div、20A/div 和 2μs/div。 图 12在全功率下采集的电感器电流波形(I LA和 I LB)和 GaN FET V DS波形:(a) V IN <V OUT /2,(b) V IN = V OUT /2,以及 (c) ) V输入? V输出/2。资料德州仪器图 13显示了在整个负载范围内以 230V交流输入运行的系统的测量效率和 THD 。 图 13在整个负载范围内使用 230V交流输入运行的两相 PFC 的效率和 THD 。资料德州仪器