模拟 IQ 调制器(用于发射器)和 IQ 解调器(用于接收器)已经使用了几十年([1] 到 [3])。

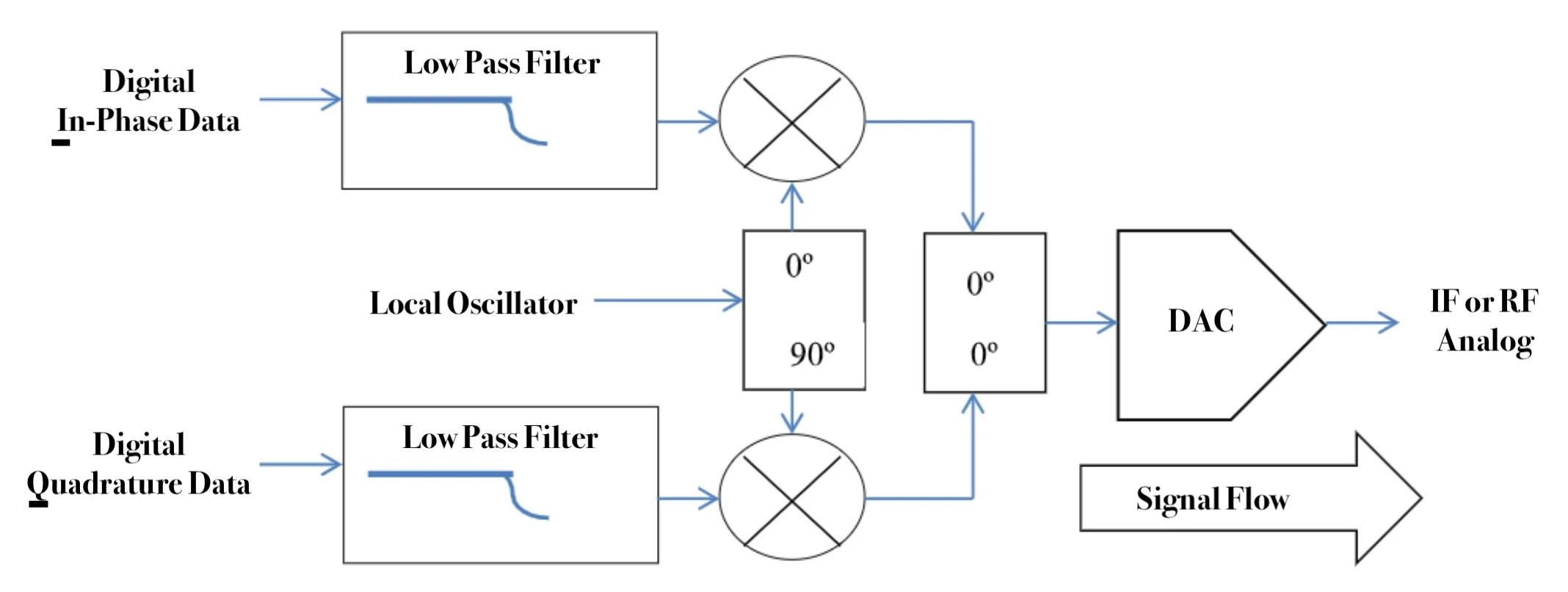

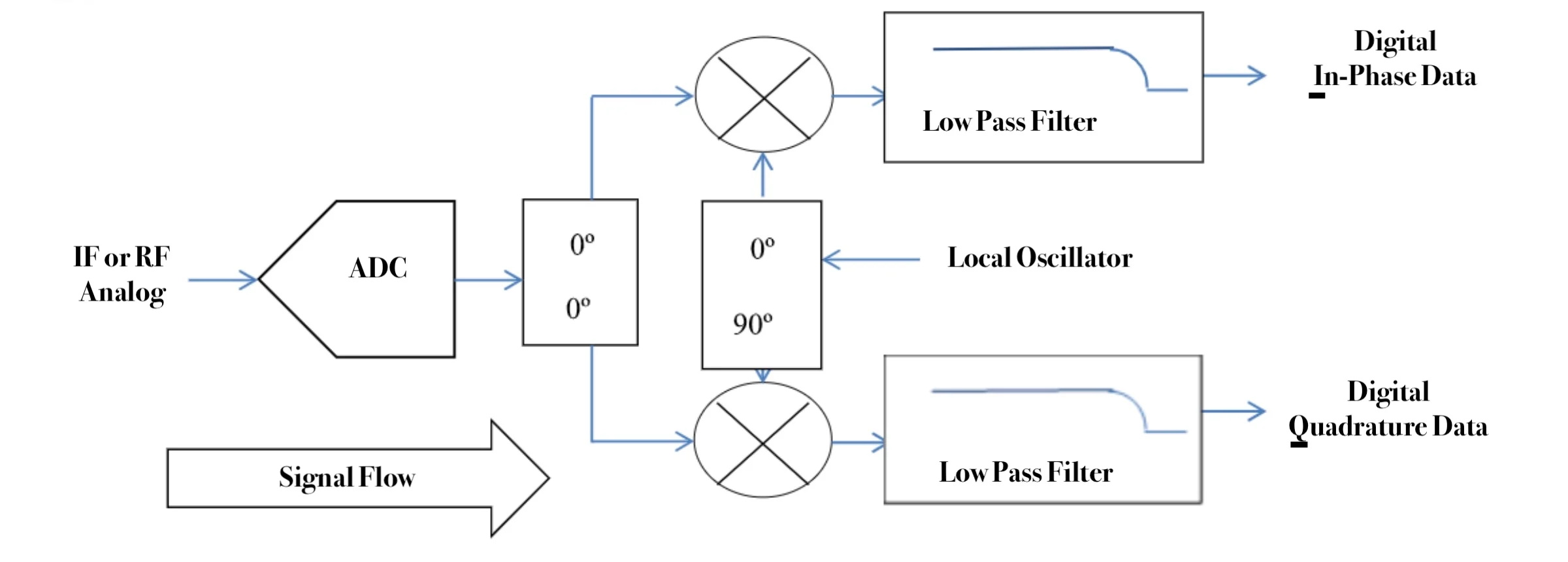

近推出了新的 A/D 和 D/A 转换器,可以直接对 1 到 4 GHz 的 IF 进行采样;在第 2、第 3 和第 4 奈奎斯特区([4] 至 [7])中采样。这些与更高速的数字逻辑相结合,允许以数字方式完成组合(对于 A/D)和分离(对于 D/A)([8] 至 [21])。这在图 1(a)(对于调制器)和图 1(b)(对于解调器)中进行了说明,数据转换器(DAC 或 ADC)位于“D”位置。

图 1(a)。 调制器

图 1(b)。解调器

另一方面,集成模拟 I、Q 组合器和分离器在 I 和 Q 路径之间具有非常好的匹配,解决了一些反对模拟执行这些过程的问题。模拟技术还需要两倍于中频直接采样的数据转换器(A/D 或 D/A),但它们以较低的采样率运行;因此它们更便宜并且需要更少的功率。这在图 1(a)(对于调制器)和图 1(b)(对于解调器)中进行了说明,数据转换器(DAC 或 ADC)位于“A”位置。

笔者开始思考这个问题。他在几个 LinkedIn 群组中征求意见,并获得了有价值的答案。经致谢者同意,现致谢如下。他还找到了关于这些功能的现代集成电路 (IC) 属性的所有信息,以及为这些 IC 确定的任何性能要求的结果。由此,他试图得出任何可以得出的一般性结论来回答这个问题;“IQ 调制和解调应该模拟还是数字方式完成?”

模拟智商方法

模拟 IQ 方法已经存在了几十年([1] 到 [3])。任何 IF 或 RF 信号都可以表示为

R(t) = I(t)cos(2πft) +Q(t)sin(2πft)

其中 f 是载波频率,I(t) 称为同相分量,Q(t) 称为正交分量。模拟 IQ 调制器采用基带信号 I(t) 和 Q(t) 并形成 R(t)。如图 1(a) 所示,DAC 位于位置 A。模拟 IQ 解调器将输入 R(t),并形成 I(t) 和 Q(t)。如图 1(b) 所示,DAC 位于位置 A。

模拟方法的一个关键问题是保持两条路径的增益相同,相位差恰好为 90?。有时会因为这些要求而忽略两个低通滤波器。对于具有显着信号能量的所有频率,它们应该增益和相位匹配。这些要求的更的量化,以及与它们的偏差造成的损害,将在后面的文章中显示。

数字智商方法

高速数据转换器(DAC 和 ADC)的发展使人们通过数字方式实现 IQ 调制器和解调器功能来避免模拟 IQ 方法部分中讨论的 IQ 不平衡问题,其中增益和相位可以在没有错误([5]、[8] 到 [21])。对于调制器情况,输出端有一个高速 DAC,如图 1(a) 所示,DAC 位于位置 D。对于解调器情况,输入端有一个高速 ADC,如图 1(a) 所示图 1(b) 中 ADC 在位置 B。

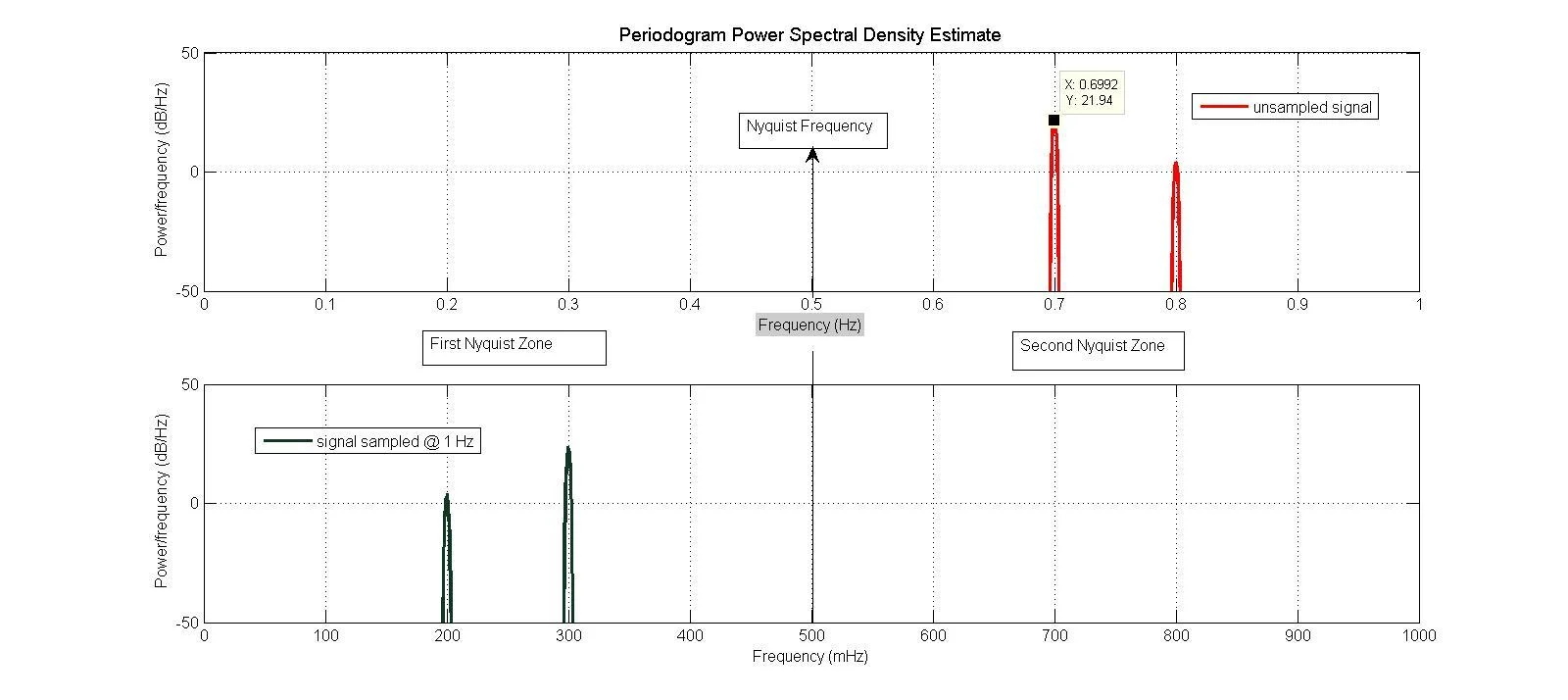

通常,这些数字方法利用混叠效应,使用所谓的带通采样([22] 至 [24]。[24A],[24B])。图 2(a) 显示了及时采样的波形。图 2(b) 显示了未采样和采样信号的频谱。ADC 的采样时钟执行与 RF 混频器中的本地振荡器相同的功能。对于 ADC,模拟滤波器只能允许一个奈奎斯特区中的信号通过,并且这种混频操作可用于将该奈奎斯特区中的信号下变频至基带。

图 2(a)。时域采样

图 2(b)。未采样和采样信号的频谱

对于 DAC,可以及时对输出进行整形,以提高更高频率下的性能。

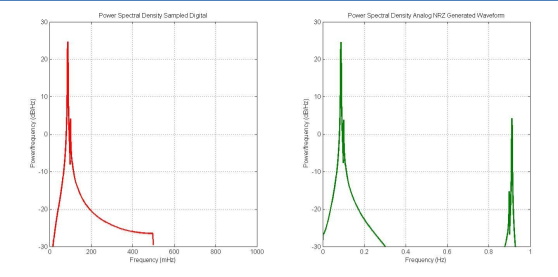

图 3(a) 显示了“正常”或“不归零”(NRZ) DAC 输出。在每个样本之后,输出保持不变,直到下一个样本。模拟频谱如图 3(b) 所示。

图 3(a)。时域采样

图 3(b)。

图 4(a) 显示了“归零”(RZ) DAC 输出。每次采样后,输出在半个采样周期内保持不变,然后变为零。这会增加第二奈奎斯特区的幅度,如图 4(b) 所示。

图 4(a)。时域采样

图 4(b)。

图 5(a) 显示了“混合”或“RF”DAC 输出。在每个样本之后,输出在半个样本周期内保持不变,然后变为负值。这与使用本地振荡器波形的两个极性的混频器的操作相同。如图 5(b) 所示,模拟频谱在第二奈奎斯特区具有更大的振幅。通过上述任何方法创建波形后,必须使用低通或带通滤波器滤除所需频率,以消除可能存在的任何不需要的混叠和杂散响应。

图 5(a)。时域采样

图 5(b)。

数字方法避免了正交失衡的任何问题。然而,由于量化和采样效应,所有数据转换器都有自己的不良影响。其中一些效果将在下一篇文章中展示。与模拟 IQ 网络相比,这些高速数据转换器的成本和功率要求通常也很高。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。