传统的倍频器需要很多元件:一个相位比较器来检测输入和输出信号之间的相位误差,一个低通滤波器将相位误差转换为直流控制信号,一个 VCO 来产生输出,一个分频器来设置提高倍数。图 1 中的电路 使用不同的方法以 1 到 7 的可编程倍率倍频(表 1)。因为电路是边沿触发的,所以 50% 的输出占空比与输入波形的占空比无关。测试结果表明,输出频率范围从31 Hz到大于30 kHz。

基于 C 的倍频电路

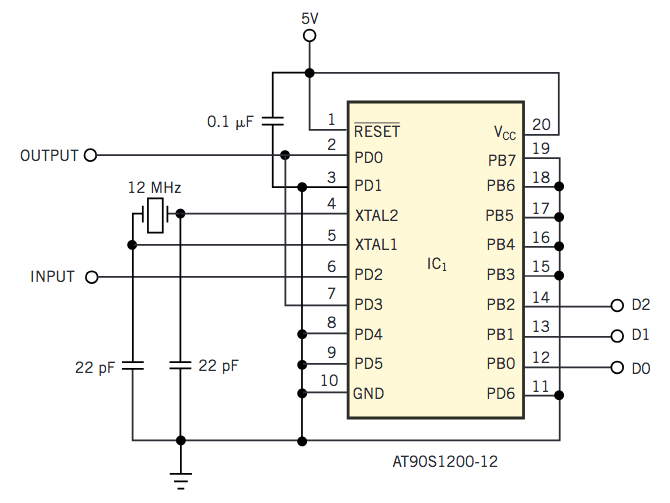

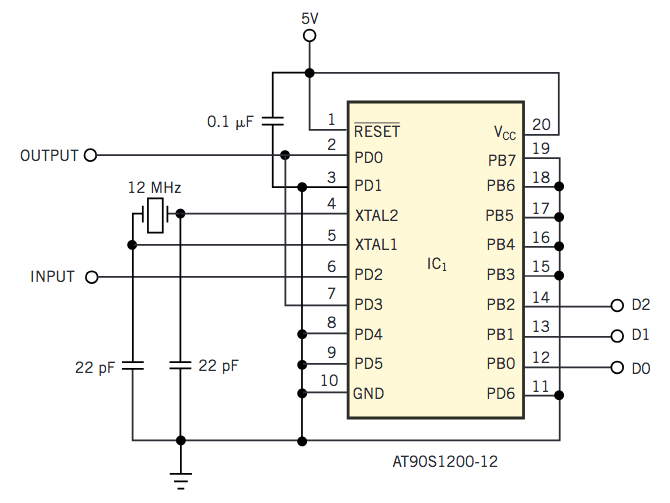

图 1 一个简单的基于C 的电路可以将频率乘以 1 到 7。

AT90S1200 是一款低成本、高速的 ?C,大多数指令只需要一个时钟周期。使用 12 MHz 的时钟,这些指令需要 83.3 纳秒。这个数字对输入频率设置了上限,因为软件执行所有功能。清单 1中的程序包括一个无限循环以生成方波输出。输出频率取决于 16 位延迟寄存器的值,该寄存器包含两个 8 位寄存器:dly_1 和 dly_2。延迟函数是一个倒计时循环,直到它达到零。延迟寄存器中的数字越大,延迟时间越长。无限循环和延迟寄存器的功能类似于压控

振荡器。

AT90S1200 有一个 8 位

计数器,其输入是输出信号。因为这个计数器是一个递增计数器,所以可编程倍数比率以 2 的补码格式加载到计数器中。例如,如果倍频比为 4,则软件会用 0xfc 加载该计数器。因为计数器的初始值为0xfc,四个输出脉冲导致计数器溢出,从而产生中断。该计数器的功能类似于传统倍频器中的分频器。

输入信号的每个上升沿也会产生一个中断。因此,中断子程序必须识别触发中断的事件。如果输入导致中断,则输出的频率太低。如果计数器触发中断,说明输出频率过高。在这两种情况下,软件都必须相应地调整延迟寄存器的值。中断子程序类似于相位比较器。