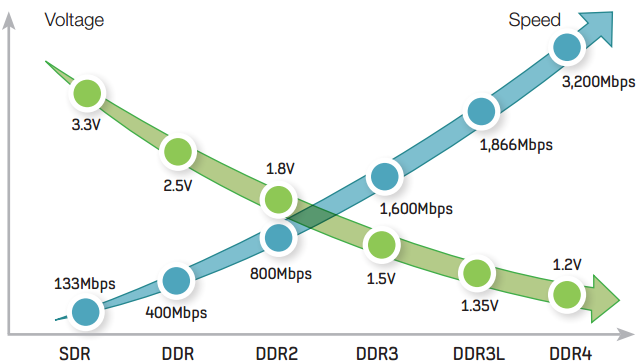

究竟什么是高速电路呢?在过去的低速时代,电平跳变时信号上升时间较长,通常有几个ns。器件间的互连线不至于影响电路的功能,没必要关心信号完整性问题。但在今天的高速时代,随着IC输出开关速度的提高,很多都在皮秒级,不管信号周期如何,几乎所有设计都遇到了信号完整性问题。另外,对低功耗追求使得内核电压越来越低,DDR4 1.2v内核电压已经很常见了。因此系统能容忍的噪声余量越来越小,这也使得信号完整性问题更加突出。

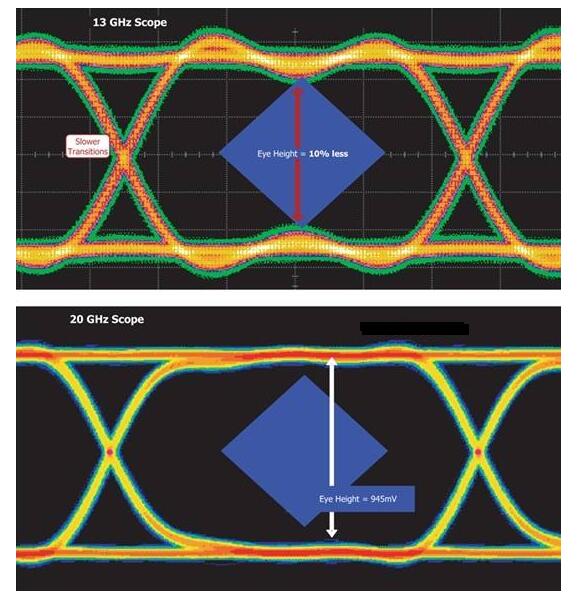

信号完整性问题的根源在于信号上升时间的减小。即使布线拓扑结构没有变化,如果采用了信号上升时间很小的IC芯片,现有设计也将处于临界状态或者根本就停止工作。

1.高速电路的定义

狭义的理解是,通常认为数字逻辑电路的频率达到或者超过50MHz,而且工作在这个频率之上的电路已经占到了整个电子系统相当的分量,例如三分之一,就称为高速电路。而实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿引发了信号传输的各种问题。所以,当信号所在的传输路径长度大于1/6倍传输信号的波长时,信号被认为是高速信号;当信号沿着传输线传播时,发生了严重的趋肤效应和电离损耗时,认为是高速信号。因此,通常约定如果电路板上信号的传播延迟大于一半数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应,这样的电路就是高速电路。

2.高速与高频区别及联系

大多数的信号完整性书籍,在进行信号完整性研究之前,一般都会先来介绍高速与高频这两个基本概念,从这一点可以知道区分这两个概念的重要性,因为,通过这两个概念可以明确信号完整性分析的对象。对于,高频这个概念理解起来比较简单,它只是对频率的一种描述,大家知道,频率是周期的倒数,高频是高频率,短周期的表述。

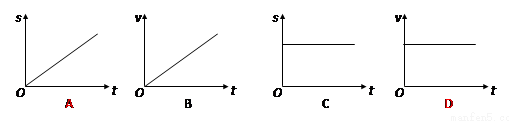

再说高速这个概念,回归到速度的概念,速度是表征运动快慢的物理量,在物理学里是位移对时间的微分,也就dS/dt。同样可以应用在电路中指的是,电位移对时间的微分,表征为电压变化的快慢,也就dV/dt,通常我们会表述为上升时间。所以,高速电路是电压变化快,上升时间短的表述。在电路系统中,上升时间的大小对于信号完整性的影响非常大,也是引起信号完整性问题的根源所在。以至于信号完整性分析基本上都是围绕dV/dt来分析和讨论的,而不是对于周期来讨论,这也是高速与高频的本质区别。

所以,从上面对两个概念的描述,可以了解到,高频与高速并没有直接的关系。可以正反举几个例子。例如,当一个时钟信号的频率为50MHz,上升时间为90ps,那么它不是一个高频信号,但它是一个高速信号,也就是频率不高,但上升沿快。又比如,频率为500MHz,上升时间为0.8ns,那么它与上例中信号相比较,频率要高很多,但速度却远比上例的信号低。所以,我们说,信号的高频与高速没有之间的关系。

从另一个角度来看,高速与高频果真没有半毛钱关系吗?其实不然,大家通常会将这两个概念混淆正是因为它二者存在千丝万缕的联系。具体说来,就是随着频率的升高,周期减小,所带来的结果是,我们必须把速度做高,原因是我们必须保证足够的建立时间与保持时间。随着周期的压缩,要想有足够的建立时间与保持时间,就只能使上升时间与下降时间缩短,以此来满足信号的时序有效性的要求。举个栗子,一个信号的频率为100MHz,即周期为10ns,上升时间与下降时间分别为1ns,这样信号的有效采样时间窗口为:(10-1-1)ns,即8ns。如果此信号的频率提高到200MHz时,保持上升时间与下降时间不变的话,采样窗口就变成了(5-1-1)=3ns,而且随着频率的继续升高,采样窗口会继续降低,极端情况会导致无法正确的采样,于是就迫使上升时间与下降时间减小,来满足越来越高的采样时钟频率。总结成一句话,也就是频率的升高必然迫使速度的提高,高频电路的进化导致了高速电路,高频与高速之间是充分条件,而不是必要条件。另外,在信号完整性的分析过程中, 一般着重强调的是高速电路。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。