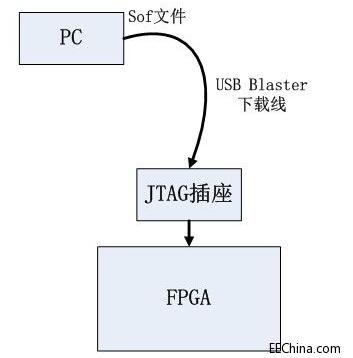

图2.21 JTAG方式配置过程

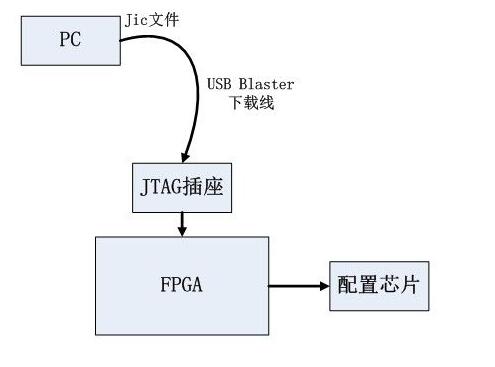

FPGA数据到配置芯片的原理如图2.22所示,PC端的Quartus II软件通过线缆将配置数据流(jic文件)到配置芯片中。由于配置芯片和JTAG接口都是分别连接到FPGA的,他们不是直接连接,所以配置文件从PC先是传送到FPGA,然后FPGA内部再转送给配置芯片,这个过程FPGA相当于起到一个桥接的作用。

图2.22 JTAG方式数据到配置芯片

看完JTAG模式下在线配置FPGA和烧录配置芯片的原理,我们再了解一下FPGA上电初始的配置过程。FPGA上电后,内部的控制器首先工作,确认当前的配置模式,如果是外部配置芯片启动,则通过和外部配置芯片的接口(如我们的SPI接口)将配置芯片的数据加载到FPGA的RAM中,配置完成后开始正式运行。当然了,有人可能在想,JTAG在线配置是否和配置芯片加载相冲突呢?非也,JTAG在线配置的优先级是的,无论此时FPGA中在运行什么逻辑,只要JTAG启动,则FPGA便停下当前的工作,开始运行JTAG的新的配置数据。

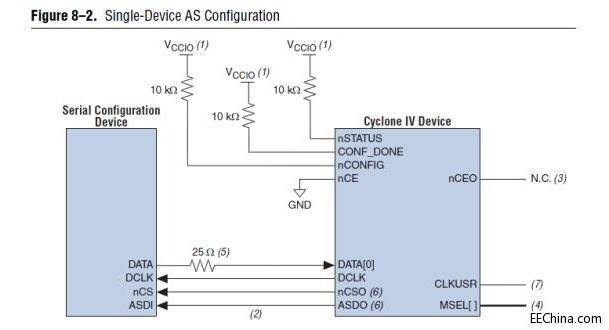

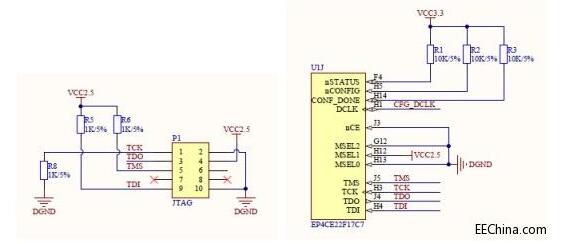

先看器件手册中给出的一些相关参考设计,如图2.23所示,这是FPGA和用于配置的SPI Flash的接口连接方式,即我们所说的AS配置方式。注意FPGA的几个主要引脚nSTATUS\CONF_DONE\nCONFIG\nCE的连接,或者上拉,或者接地,主要是为了保证这些信号在上电初始处于一个确定的电平状态,防止错误电平导致误触发。DATA\DCLK\NCSO\ASDO这4个引脚便是SPI接口,连接到SPI Flash。

图2.23 AS配置参考电路的截图

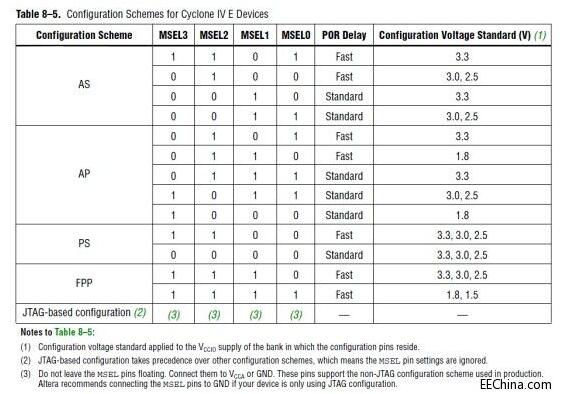

如图2.24所示,FPGA有组MSEL引脚是用于设置FPGA初上电时的启动模式,我们的FPGA上电使用Standard AS模式从SPI Flash里面加载配置数据。

图2.24 MSEL引脚配置说明的截图

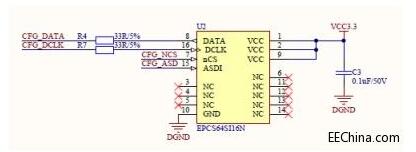

有了前面的理论做铺垫,我们的设计也就有依有据了。如图2.25所示,这是我们的SPI FLASH芯片,它的4个信号分别连接到FPGA器件的相应引脚上。

图2.25 FPGA的AS配置电路

前面是上电启动配置数据的电路,通过一个SPI Flash来实现。而PC端到FPGA器件的则是通过JTAG来实现的,JTAG这个概念网络上满天飞了,大家自己去消化,但凡有CPU的地方,基本都有JTAG的存在,FPGA也不例外。另外,大家注意前面的MSEL设置了FPGA启动模式是Standard AS模式,但是JTAG永远是优先级的模式,任何时刻,只要JTAG需要进行配置,那么配置模式将会转换。JTAG插座以及部分配置专用引脚的连接电路如图2.26所示。

图2.26 JTAG插座与FPGA配置电路

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。