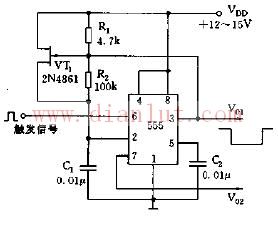

如图所示,该电路的输入脉冲为正触发信号,输出两路为负定时脉冲。当触发脉冲来时,555复位,输出低电平,C1通过R2灌入集成块内放电,R2C1的放电时间决定了输出负向脉冲宽度。当C1上电压放至低于1/3VDD触发电平(2脚)时,555置位,3脚呈高电平,VTl饱和导通,电源对C1充电,因而该电路定时高,占空比可达99%,且波形好。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。