在数字系统中,为了使各部分在时间上协调动作,需要有一个统一的时间基准。用来产生时间基准信号的电路称为时基电路。555集成定时器就是其中的一种。它是一种由模拟电路与数字电路组合而成的多功能的中规模集成组件,只要配少量的外部器件,便可很方便的组成触发器、振荡器等多种功能电路。因此其获得迅速发展和广泛应用。

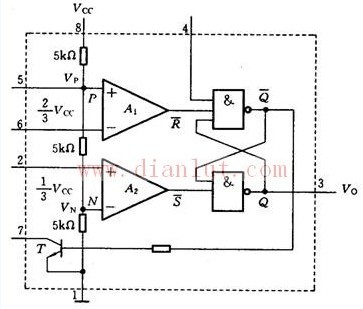

555集成定时器的工作原理如下:如图所示为其内部电路结构图。整个电路包括分压器,比较器,基本RS触发器和放电开关四个部分。

(1)分压器 由三个5kΩ的电阻串联组成分压器,其上端接电源VCC(8端),下端接地(1端),为两个比较器A1、A2提供基准电平。使比较器A1的“+”端接基准电平2VCC/3(5端),比较器A2的“-”端接VCC/3。如果在控制端(5端)外加控制电压。可以改变两个比较器的基准电平。不用外加控制电压时,可用0.01μF的电容使5端交流接地,以旁路高频干扰。

(2)比较器A1、A7是两个比较器。其“+”端是同相输人端,“-”端是反相输入端。由于比较器的灵敏度很高,当同相输入端电平略大于反相端时,其输出端为高电平;反之,当同相输入端电平略小于反相输人端电平时,其输出端为低电平。因此,当高电平触发端(6端)的触发电平大于2VCC/3时,比较器A1的输出为低电平;反之输出为高电平。当低电平触发端(2端)的触发电平略小于VCC/3时,比较器A2的输出为低电平;反之,输出为高电平。

(3)基本RS触发器 比较器A1和A2的输出端就是基本RS触发器的输入端RD和SD.因此,基本RS触发器的状态(3端的状态)受6端和2端的输入电平控制。图中的4端是低电平复位端。在4端施加低电平时,可以强制复位,使Q=0.平时,将4端接电源VCC的正极。

(4)放电开关图中晶体管VT构成放电开关,使用时将其集电极接正电源,基极接基本RS触发器的Q端。当Q=0时,VT截止;当Q=1时,VT饱合导通。可见晶体管VT作为放电开关,其通断状态由触发器的状态决定。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。