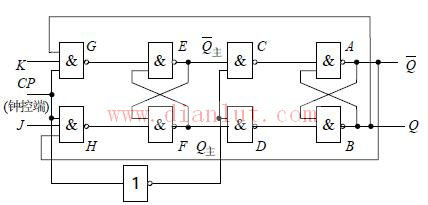

主从JK触发器电路

如图为主从JK触发器电路图。JK触发器,采用与或非电路结构,它的工作原理为:CP为0时,触发器处于一个稳态;CP由0变1时,触发器不翻转,做好接收输入信号的准备;CP由1变0时触发器翻转;JK触发器在CP下降沿前接受信息,在下降沿触发翻转,在下降沿后触发器被封锁。

主从JK 触发器是在主从RS触发器的基础上组成的。在主从RS触发器的R端和S端分别增加一个两输入端的与门,将Q端和输入端经与门输出为原S端,输入端称为J端,将Q端与输入端经与门输出为原R端,输入端称为K端。

主从JK触发器工作原理

由上面的电路可得到S=JQ,R=KQ。代入主从RS触发器的特征方程得到:

J=1,K=0时,Qn+1=1;

J=0,K=1时,Qn+1=0;

J=K=0时,Qn+1=Qn;

J=K=1时,Qn+1=-Qn(Qn非);

由以上分析,主从JK 触发器没有约束条件。在J=K=1时,每输入一个时钟脉冲,触发器翻转。触发器的这种工作状态称为计数状态,由触发器翻转的次数可以计算出输入时钟脉冲的个数。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。