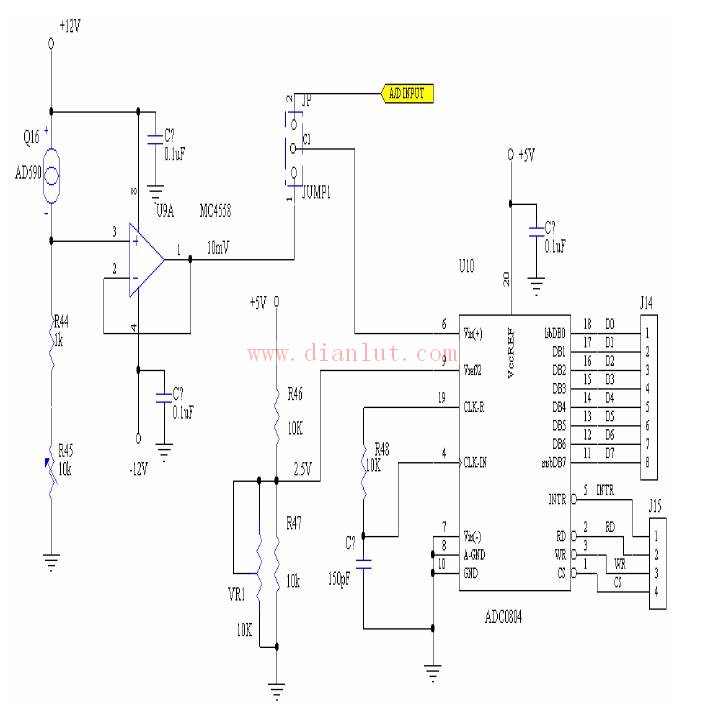

A/D电路以两种方式输入讯号,这两种方式的切换由JUMP1来连成,拨上输入由USER自己供给,拨下则由AD590温度感测器來输入讯号,J14、J15分别为输出资料脚及控制脚。

ADC0804

引脚功能及应用特性如下:

CS 、RD 、WR (引脚1、2、3):是数字控制输入端,满足标准TTL 逻辑电平。其中CS 和WR 用来控制A/D 转换的启动信号。CS 、RD 用来读A/D 转换的结果,当它们同时为低电平时,输出数据锁存器DB0~DB7 各端上出8 位并行二进制数码。CLKI(引脚4)和CLKR(引脚19):ADC0801~0805 片内有时钟电路,只要在外部CLKI”和“CLKR”两端外接一对

电阻电容即可产生A/D 转换所要求的时钟,其振荡频率为fCLK≈1/1.1RC。其典型应用参数为:R=10KΩ,C=150PF,fCLK≈640KHZ,转换速度为100μs。若采用外部时钟,则外部fCLK 可从CLKI 端送入,此时不接R、C。允许的时钟频率范围为100KHZ~1460KHZ。INTR (引脚5): INTR 是转换结束信号输出端,输出跳转为低电平表示本次转换已经完成,可作为

微处理器的中断或查询信号。如果将CS 和WR 端与INTR 端相连,则ADC0804 就处于自动循环转换状态。CS =0 时,允许进行A/D 转换。WR 由低跳高时A/D 转换开始,8 位逐次比较需8×8=64 个时钟周期,再加上控制逻辑操作,转换需要66~73 个时钟周期。在典型应用fCLK=640KHZ 时,转换时间约为103μs~114μs。当fCLK 超过640KHZ,转换下降,超过极限值1460KHZ 时便不能正常工作。