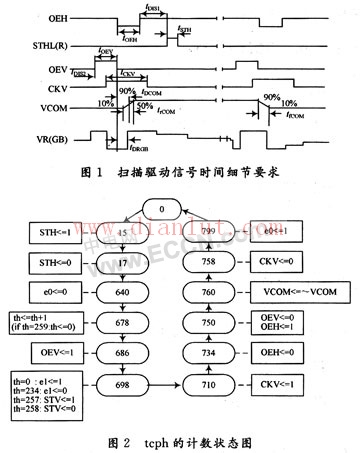

图中所有时间间隔均为CPH的整数倍,因此用计数器tcph对CPH计数,判断tcph的值便可产生其他控制信号,同时保证各路信号同步。各接口信号时间要求在AT056TN04的手册中已经给出,CPH是整个时序中的单元,其周期为154 ns,误差不能超过4 ns.采用13 MHz的有源晶振,时钟周期为76.9 ns,对其进行2分频,得到153.8 ns的CPH时钟。AT056TN04每帧数据包含256~268行,真正的显示行数是234行,其中的少部分行是不显示数据的。外部控制器可以在这些不显示数据的行里对显示存储器进行读写操作。本设计的每帧数据显示行数设定为260行,那么STV就是每隔260行会产生一个脉冲,用一个行计数器th,当tcph为260(即一行显示完)后th加1,以产生STV,STV出现后要延时tsv(3行)。每行时间设计为800个CPH,tcph的计数状态如图2所示。

3液晶屏刷新模块设计

AT056TN04配置为从左到右从上到下的扫描方式,每次读入存储8个点的三色信息(3 B),每个CPH时钟下RGB三字节数据同时向左移动一位,在PFGA的RGB输出脚接4.7 kΩ的上拉电阻到5 V电源,产生VR,VG,VB信号驱动液晶屏。在RAM读写控制模块和时序模块的作用下控制器将显示RAM中的图像数据循环的送到液晶屏上显示。使用计数器th和tcph就可以方便产生地址,从而实现对RAM(RAM(随机存取存储器)RAM -random access memory 随机存储器。存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。 按照存储信息的不同,随机存储器又分为静态随机存储器(Static RAM,SRAM)和动态随机存储器(Dynamic RAM,DRAM)。)的读写操作。其中th值作为行地址用,tcph[9:4]作为列地址,tcph[1:0]作为颜色地址。

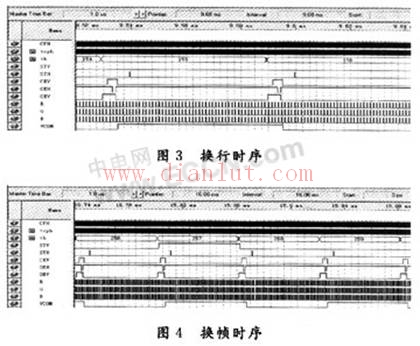

在QuartusⅡ中的仿真结果如图3,图4所示,其中图3是换行时的各信号的波形,图4是换帧时各信号的波形。从结果可以看出,波形完全满足设计要求。

4结 语

在合理的存储器安排和行列计数器设计基础上,巧妙地完成液晶时序控制和显示存储器数据的读写,实现对AT056TN04的8种基本颜色的显示控制。由于采用FPGA设计,稍加修改便能以软核的形式应用于其他液晶模块,克服了单色液晶模块色彩单调,而颜色丰富的数字彩色屏价格贵的缺点。对颜色要求不高的工业仪器仪表中具有一定的应用价值。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。