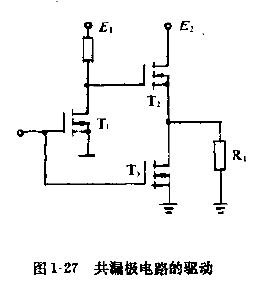

VMOS管共漏极组态的驱动要比共源极组态的驱动困难些,但还是比双极晶体管共集电极组态的驱动容易。当需要负载一端接地时,或者需要有源推-拉输出电路时, 常采用共漏极电路。这种电路的驱动出现闲难,是因为随着负载上电压的升高,共漏极器件的增强电压降低。参看图1-27,随着负载RL上电压接近电源电压E2管T2的增强电压下降。加果E1不大于E2,那么RL上的电压总也达不到E2。

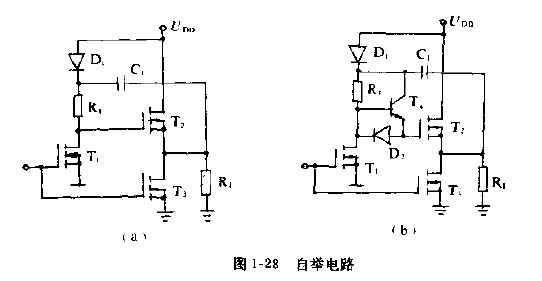

产生所需栅压的一种办法是自举电路,如图1-28(a) 所示。该电路中,当VMOS管T1和T3导通时,通过二极管D1.电容C1被充电到电源电压。当T1和T3截止时,管T2的栅极电压达到电源电压。由于T2的源极使RL电平上拉,C1上电压将保持不变,所以T2的栅源电压也将保持不变。C1 容量应足够大,以保证当它给T2的栅极电容充电时,电容器上的电压也能等于T2所需的增强电压。通常,选取C1容量大于VMOS管输人电容C的10倍。

图1-28(b)电路是在图1-28(b)基础上改进而成,它增加若干元器件以进一歩改善上升时间和下降时间。图1-28(b)中,T4为射随器,用来向T2提供较大的峰值栅极电流,以改善输出脉冲的上升时间。当T1导通时,二极管D2正向偏置,于是给栅极电容放电提供一低阻回路,减少了输出脉冲的下降时间。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。