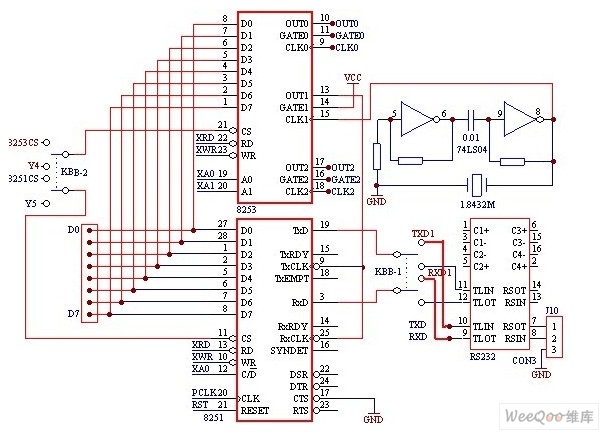

基于单片机的双机通信设计电路图如下所示:

如图所示,TXC和RXC分别为8251A的发送时钟和接收时钟。它由片外8253A的OUT1提供。本实验要求以查询方式进行收发。要完成本实验,需2台DVCC系列实验系统。其中一台为串行发送,一台为串行接收,在1号机上装串行发送程序,在2号机上装串行接收程序,则在1号机上键入的字符显示在2号机的显示器上。

由于本系统监控中未对8253A、8251A进行初始化,因此本实验开始必须对8253、8251进行初始化,然后才可以直接进入对串行口状态的查询。

程序

系统晶振是 6.0 MHz

ORG 07F0H

START:

MOV SP,#60H

mov A,#02H

MOV R0,#79H

MOV @R0,A

INC R0

MOV A,#10H

MOV @R0,A

INC R0

MOV A,#01H

MOV @R0,A

INC R0

MOV A,#03H

MOV @R0,A

INC R0

MOV A,#00H

MOV @R0,A

INC R0

MOV A,#08H

MOV @R0,A

MOV A,#7EH

MOV DPTR,#1FFFH

MOVX @DPTR,A

MOV 87H,#80H

MOV SCON,#50H ;串口 方式 1

MOV TMOD,#20H ;T1 方式 1

MOV TL1,#0F3H ;波特率 9600 的常数

MOV TH1,#0F3H

SETB TR1 ;开中断

CLR ET1

CLR ES

WAIT:

JBC RI,DIS_REC ;是否接收到数据

LCALL DISP ;

SJMP WAIT ;

DIS_REC:

MOV A,SBUF ;读串口接收到的数据

LCALL DATAKEY ;显示输入的数字(0-F)

DB 79H,7EH

AJMP WAIT

DATAKEY: MOV R4,A

MOV DPTR,#1FFFH

MOVX A,@DPTR

MOV R1,A

MOV A,R4

MOV @R1,A

CLR A

POP 83H

POP 82H

MOVC A,@A+DPTR

INC DPTR

CJNE A,01H,DATAKEY2

DEC R1

CLR A

MOVC A,@A+DPTR

DATAKEY1: PUSH 82H

PUSH 83H

MOV DPTR,#1FFFH

MOVX @DPTR,A

POP 83H

POP 82H

INC DPTR

PUSH 82H

PUSH 83H

RET

DATAKEY2: DEC R1

MOV A,R1

SJMP DATAKEY1

DISP: SETB 0D4H

MOV R1,#7EH

MOV R2,#20H

MOV R3,#00H

DISP1:

MOV DPTR,#DATACO

MOV A,@R1

MOVC A,@A+DPTR

MOV DPTR,#0FF22H

MOVX @DPTR,A

MOV DPTR,#0FF21H

MOV A,R2

MOVX @DPTR,A

LCALL DELAY

DEC R1

CLR C

MOV A,R2

RRC A

MOV R2,A

JNZ DISP1

CLR 0D4H

RET

DELAY: MOV R7,#03H

DELAY0: MOV R6,#0FFH

DELAY1: DJNZ R6,DELAY1

DJNZ R7,DELAY0

RET

DATAC DB 0C0H,0F9H,0A4H,0B0H,99H,92H,82H,0F8H,80H,90H

DB 88H,83H,0C6H,0A1H,86H,8EH,0BFH,0CH,89H,0DEH

END

实验步骤

1、准备2台DVCC系列实验仪,确定1号为发送,2号为接收。

2、将1号RXD插孔和2号的TXD插孔相连。

3、将1号TXD插孔和2号的RXD插孔相连。

4、将1号GND插孔和2号的GND插孔相连(共地)。

5、将8253CS插孔和Y4插孔相连,8251CS和Y5插孔相连。

6、将SIO区D0—D7和BUS2区 XD0—XD7相连。

7、先运行2号机,在2号机提示符“P.....”状态下,输入0D00后,再按EXEC键进入等待接收状态,显示器显示“8251—2”。

8、再运行1号机,在1号机处于提示符“P.....”状态下,输入0E00H后,按EXEC键,进入串行发送状态。显示器显示“8251—1”。

9、在1号机的键盘上输入数字键,应在2号机显示器上显示对应数字值。

10、输入数字键后再按MON键,1号机显示“8251 good”。如果不输入数字键直接按MON键,则显示“Err”,如果双机通信不能正常进行,也显示“Err”。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。