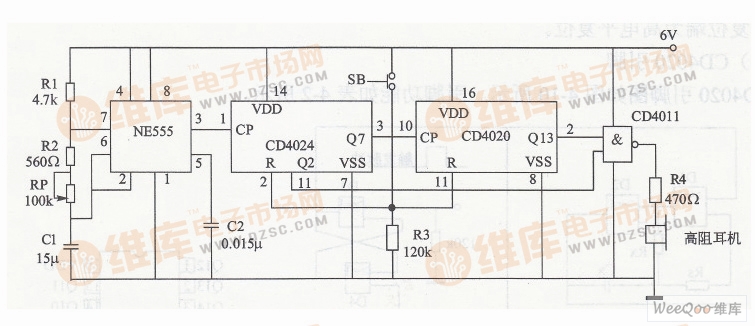

如图所示是由7位二进制串行计数器/分频器CD4024、14位二进制串行计数器/分频器CD4020以及NE555组成的定时器电路,该电路的定时范围为1~30min。

定时器电路

在电路图中,NE555与R1、R2、RP以及C1、C2组成了多谐振荡器,用来产生时基脉冲,其中RP用来调节振荡频率。CD4024组成8级分频器,其分频系数为128,CD40⒛组成14级分频器,其分频系数为8192。调节电位器RP,将NE555振荡频率上下限设定在582.5Hz~17.48kHz之间。

与非门CD4011作为缓冲器来驱动耳机发音。与非门的两端分别接CD4024的输出端Q2以及CD40⒛的输出端Q13。当超过定时时间后,从Q2端输入一个脉冲来驱动耳机发声。

当按下开关SB后,CD4024和CD4020的复位端R均接高电平,分频器发生复位,输出端全为低电平。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。