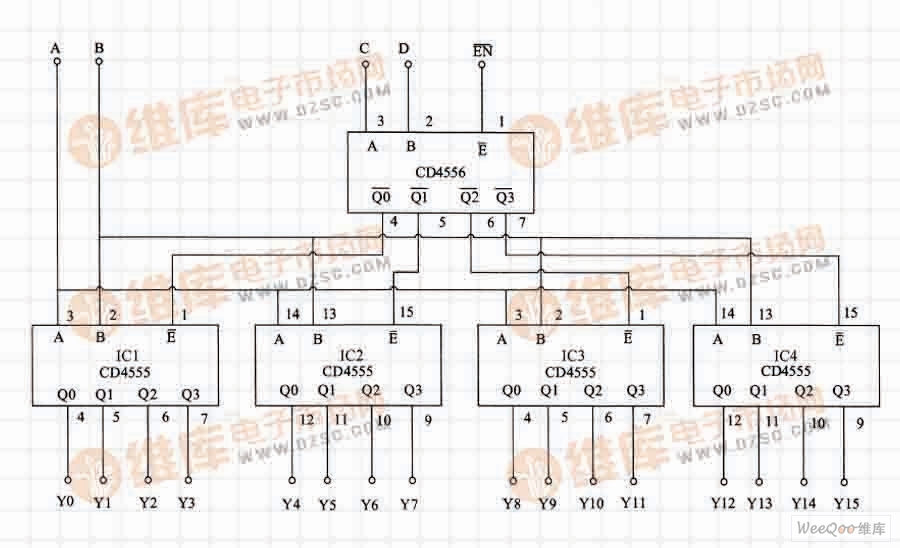

如图所示电路是由双二进制4选1译码器/分离器(输出“0”)CD4556和两片双二进制4选1译码器/分离器(输出“1”)CD4555组成的16-1线译码电路,它能实现16地址选1的功能,常用于数字系统中的多地址选择中。

16-1线译码电路

在电路图中将2片CD4555的地址输入端A、B分别并联起来,制端和CD4556的输出端也连在一起。

当CD4556的E端处于高电平状态时,它的4个输出端也为高电平状态,由4个输出端控制的CD4555的允许控制端/E也为高电平状态,此时,CD4555的译码功能不工作,所有数据输出端全为低电平状态。

当CD4556的/E端处于低电平状态时,根据它输入的不同,选择工作的CD4555也不同。假设C,D输入为06CD4556的输出端/Q/2为低电平状态,则IC3的/E也为低电平状态,因此允许这一路数据输入。C、D输入端在其他状态下,电路工作原理相同。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。