在 FAGA 系统设计中,I2C

总线是一种常用的通信方式,常被用于连接

存储器和

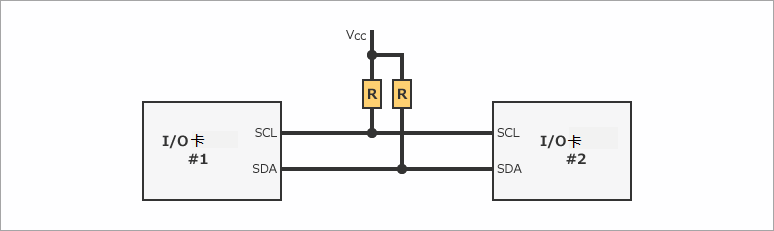

电源时序隔离芯片,在板级连接中也较为常见。I2C 总线采用简单的 2 线式连接,仅通过 1 条时钟(SCL)和 1 条数据(SDA)线来连接设备。由于其设计简单,它在通信设备中得到了越来越广泛的应用,如 SMBus、PMBus 和 ATCA 的 IPMB 总线等。

然而,尽管 I2C 总线设计看似简单,但在实际应用中,通信错误的情况并不少见。特别是在通信装置等需要与底板连接,以及在 IO 卡之间使用长配线进行通信的情况下,出现故障的可能性会显著增大。

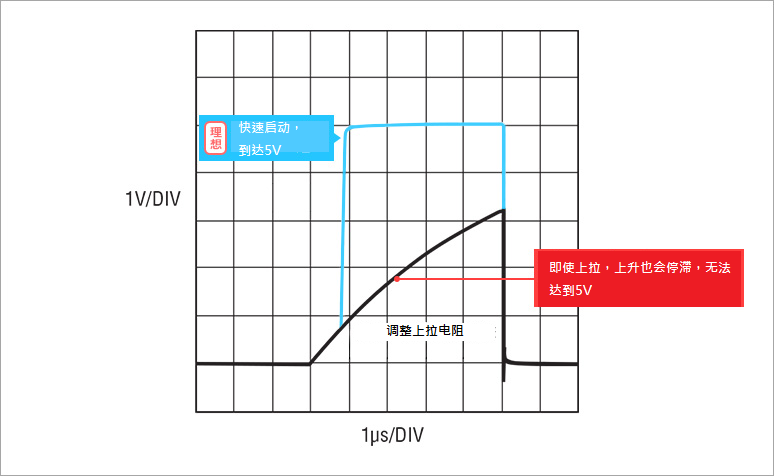

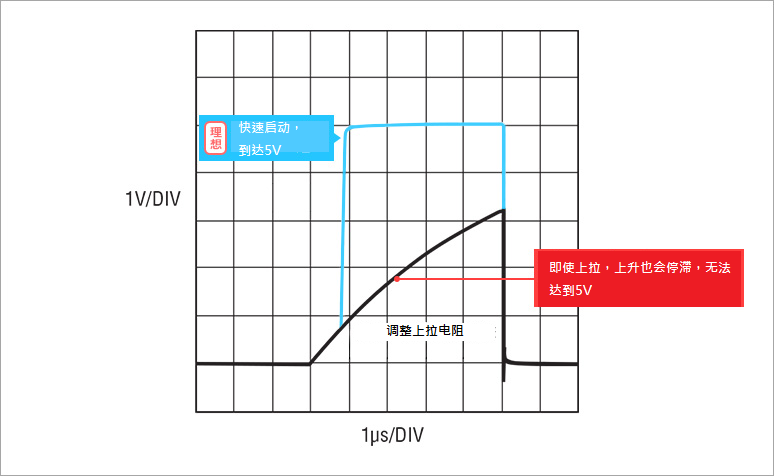

通信错误的原因分析 通信错误很可能是由于线路容量超出了 I2C 总线的规定。I2C 总线的规格明确规定,线路容量为 400pF。当进行与底板的连接,或者在 IO 卡之间采用长布线时,布线容量可能会超出 I2C 规格的限制。如图 1 所示,这会导致上升波形变钝,从而引发通信错误,因此在设计过程中需要特别注意。

图 1:上升波形

调整上拉电阻的尝试 通常情况下,针对上升沿钝化的问题,我们会采取增大上拉电流(减小上拉电阻)的措施。这样做的原理是,即使总线的寄生电容增大,也能够通过增大的上拉电流来驱动信号。然而,这种方法也存在一定的副作用。如果上拉电流过大,会导致 Low 电平上升(上拉电流 × 寄生电阻),这个上升后的电平可能会高于 VOL 的门槛电压,从而影响通信的正常进行,所以在调整上拉电阻时需要谨慎操作。

无法通过调整上拉电阻解决问题时的应对策略

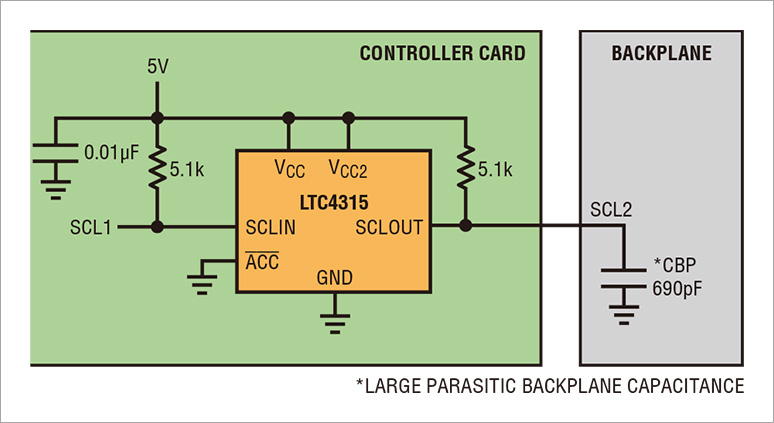

当通过调整上拉电阻无法避免通信错误时,我们需要寻找其他的解决方案。在像通信装置那样需要与底板连接的情况下,以及由于用扁平电缆连接基板间进行 I2C 总线通信,因寄生电容原因而无法避免通信错误时,使用 Analog Devices 公司的 I2C 总线缓冲区产品是一个不错的选择。

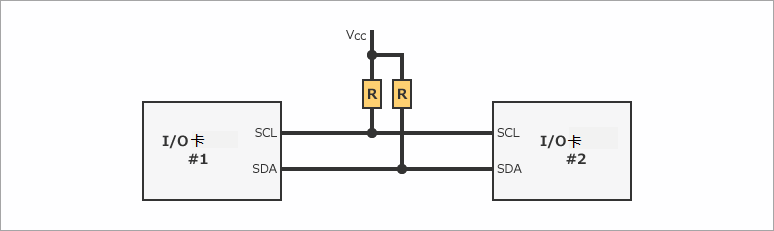

图 2:I/O 基板间的连接

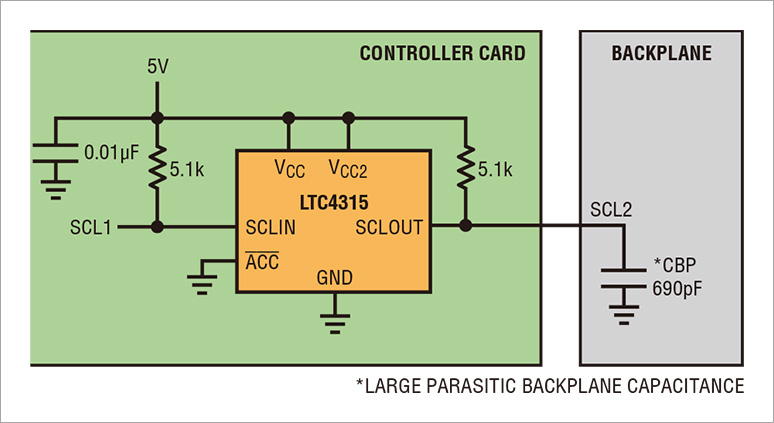

以 LTC4315 为例,它具有 Rise Time Accelerator 功能,能够有效改善逐渐消失的上升波形。如图 3 所示,将 LTC4315 放置在控制板上,即使连接到底板,也能够保证正常通信。LTC4315 可以说是 I2C 总线通信中不可或缺的产品,它能够很好地解决电路板之间(器件之间)产生较大寄生电容时的问题,从而减少通信错误的发生。

图 3:I2C 总线缓冲器

总结与建议 在使用 I2C 总线进行通信设计时,首先要充分考虑线路容量对通信的影响,尽量避免布线容量超出 I2C 总线的规格限制。在遇到上升沿钝化问题时,可以尝试调整上拉电阻,但要注意其副作用。当调整上拉电阻无法解决问题时,及时采用合适的 I2C 总线缓冲区产品,如 LTC4315,以确保通信的稳定性和可靠性。