在现代电子电路设计中,MOS 管是一种极为重要的电子元件,特别是在 DCDC(直流 - 直流)电路中,MOS 管通常作为开关管使用。在几 M 的频率下,MOS 管需要不停的进行开关动作。然而,MOS 管内部的一些寄生参数很可能会对开关动作产生影响,进而影响电源的启动时间、信号沿的过冲等性能指标。因此,深入了解 MOS 管的寄生电容是非常有必要的。

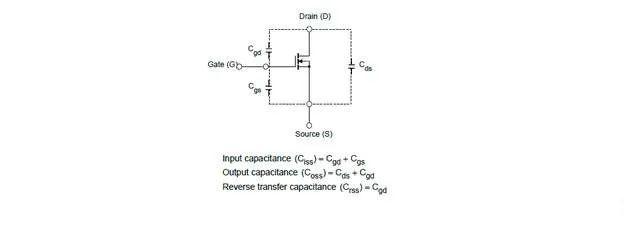

首先,让我们来看看 MOSFET 的电容等效图。

从图中可以看出,MOSFET 包含 3 个等效结电容,分别是 Cgd、Cgs 和 Cds。通常在 MOSFET 的规格书中,我们可以看到这些参数的具体信息。

- Cgs(栅源电容)

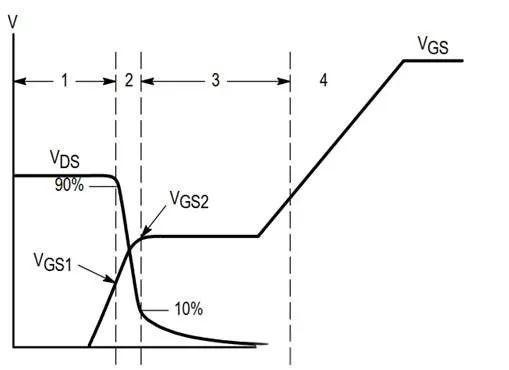

Cgs 位于栅极和源极之间,它主要由栅极与沟道之间的氧化层电容和栅极与源极的重叠电容组成。在 MOS 管的所有寄生电容中,Cgs 是的电容。由于其电容值较大,它对 MOS 管的开关速度有着显著的影响。当驱动信号对 Cgs 进行充电和放电时,较大的电容值会导致充电和放电时间变长,从而影响 MOS 管的开关速度。在设计电路时,如果需要提高 MOS 管的开关速度,就需要考虑如何减小 Cgs 的影响。例如,可以选择 Cgs 较小的 MOS 管,或者优化驱动电路,提高驱动电流,以加快 Cgs 的充电和放电过程。 - Cgd(栅漏电容)

Cgd 位于栅极和漏极之间,它由栅极与沟道之间的氧化层电容和栅极与漏极的重叠电容构成。Cgd 又被称为米勒电容,由于米勒效应的存在,Cgd 在高频和开关过程中的影响尤为显著。对于开关的上升和下降时间来说,Cgd 是一个重要的参数,它会影响关断延时时间。当 MOS 管从导通状态转变为关断状态时,Cgd 上的电荷需要通过驱动电路进行放电。由于米勒效应的作用,Cgd 上的电压变化会导致驱动电流的变化,从而影响关断延时时间。在实际应用中,为了实现电源的缓启功能,我们可以人为地并联栅漏电容。通过并联电容,可以增加 Cgd 的值,从而延长关断延时时间,实现电源的缓慢启动,减少对电路的冲击。 - Cds(漏源电容)

Cds 位于漏极和源极之间,它主要由漏极和源极之间的 PN 结电容及寄生电容组成。与 Cgs 和 Cgd 相比,Cds 的值通常较小。然而,在高频电路中,即使是较小的 Cds 也可能会对电路性能产生影响。在高频开关过程中,Cds 会在漏极和源极之间形成一个充放电回路,从而产生一定的功率损耗。此外,Cds 还可能会影响 MOS 管的输出特性,导致输出电压的波动。因此,在高频电路设计中,也需要对 Cds 进行合理的考虑和优化。