典型的 3.3 V 或 5 V 逻辑信号通常足以满足短距离芯片到芯片(即板内)通信,即使时钟频率在兆赫范围内也是如此。设计良好的 PCB 可以被认为是一个受到相当保护的环境,其中数字信号不太可能因噪声或寄生电抗而经历严重的退化。

但当数字数据(尤其是高速数据)离开这个受保护的环境时(例如,当它必须通过长

电缆或强烈的 EMI 传输到系统的单独部分时),情况就会发生变化。当存在强噪声源或需要非常高的数据速率(例如,每秒数百兆比特)时,甚至板内通信也可能成为问题。

从一根线到两根线 在这种情况下,一般的补救措施是从单端逻辑转向差分信号。RS-422/485是一个的接口,但它并未针对高速进行优化。其他选项包括电流模式逻辑 (CML) 和低压正发射极耦合逻辑 (LVPECL)。但是,根据我的经验,更常见的选择是低压差分信号 (LVDS)。

LVDS 是一种用于高速、点对点数字通信的标准化接口。 “点对点”是指一台发射器和一台接收器; LVDS 并不是为了促进系统中众多设备之间的通信,而是为了快速有效地将大量数据从一个设备移动到另一设备。

信号

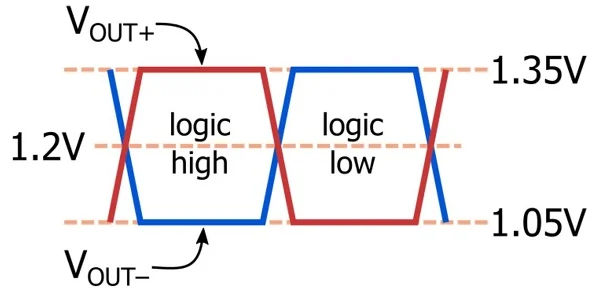

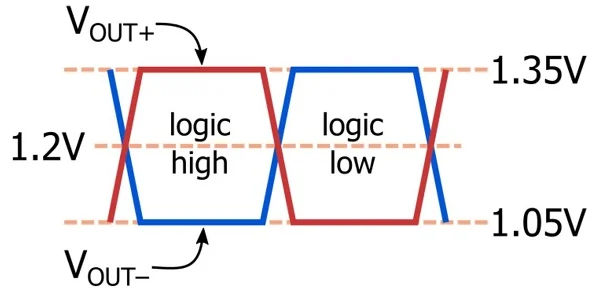

LVDS 使用(您猜对了!)低电压摆幅差分信号,如下所示:

标称共模电压为 1.2 V,差分对中每个信号的标称电压范围为高于共模电压 150 mV 至低于共模电压 150 mV。这意味着每个信号的电压仅变化 300 mV,大约比单端 3.3 V 逻辑信号的电压摆幅低一个数量级。

尽管逻辑低电平和逻辑高电平之间的电压差很小,但差分信号(与双绞线和屏蔽电缆结合使用)的优点使 LVDS 能够提供高度可靠的通信。

低压优势 低压摆幅信令不仅仅是数据完整性问题,还可以节省电力并提高速度:

端接

电阻器两端的电压越低,电流就越小,而电源电压越低,通常会降低功耗(请记住,CMOS 功耗与 VDD平方 成正比)。

电压转换不能立即发生;信号从一种电压转移到另一种电压需要时间,因此逻辑低电平和逻辑高电平之间的距离较短,可以通过减少每次逻辑转换所需的时间来实现更高频率的操作。

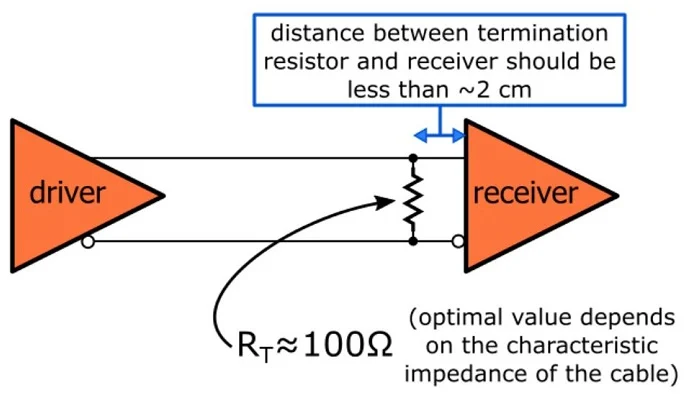

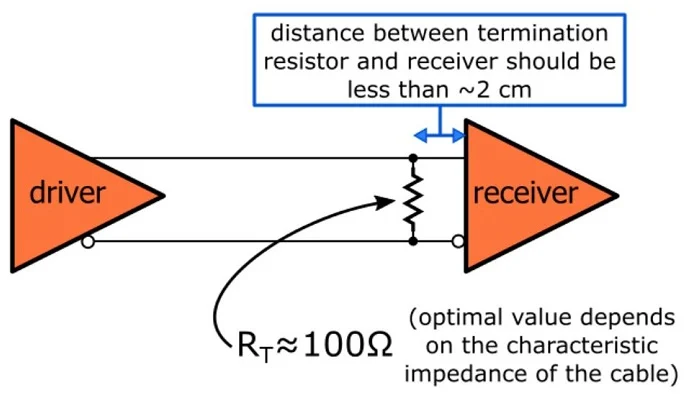

LVDS 是一种高性能标准,可以实现接近甚至超过每秒 1 GB 的数据速率(尽管速度必须随着电缆长度的增加而降低)。但不要被吓倒——大量用户友好的集成电路使 LVDS 成为一个非常平易近人的接口。使用现成的 LVDS 驱动器和接收器将标准逻辑转换为 LVDS,然后再转换回标准逻辑并不困难,而且终止也很简单:

当提供待转换信号的设备(例如

微控制器)速度太慢而无法以所需频率生成串行数据时,LVDS 就特别有价值。在这种情况下,您可以将 LVDS 串行器与 LVDS 解串器结合使用 - 前者将并行标准逻辑输入转换为串行 LVDS 输出,后者将串行 LVDS 数据转换回并行标准逻辑信号(此串行器数据表/解串器对为您提供了我所指的示例)。