低电阻路径

这个问题的基本答案是,逻辑高表示电源轨上的电压,代表二进制 1,逻辑低表示地电压,代表二进制 0。这个描述是一个很好的起点,它变得更如果我们说“靠近电源轨”和“靠近地”而不是“在电源轨处”和“在地”,那么是准确的。此修改考虑了流过 NMOS 或 PMOS 沟道的电流在源极和漏极之间产生小电压差的事实。

流经通道的电流问题会导致典型 CMOS 功能的一个更微妙但至关重要的方面。 CMOS 反相器确保输出节点与电源轨或地具有低电阻连接;反相器总是NMOS导通、PMOS截止或PMOS导通、NMOS截止。这就是为什么我们可以说 CMOS 电路驱动逻辑低或逻辑高。这也是为什么围绕

逆变器拓扑构建的

逻辑电路如此可靠的“数字”——所有节点都具有明确定义的二进制状态,因为它们始终具有通向电源电压或接地的低电阻路径。

传输

晶体管逻辑 (PTL) 也称为传输门逻辑,基于使用 MOSFET 作为

开关而不是逆变器。结果是(在某些情况下)概念上的简化,但 CMOS 反相器严格的逻辑高/逻辑低输出特性丢失了。

传输晶体管逻辑的示例

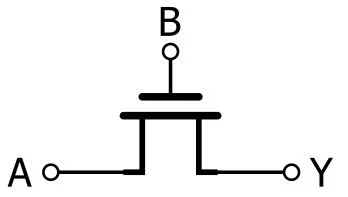

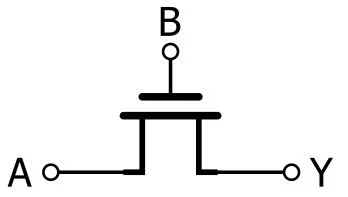

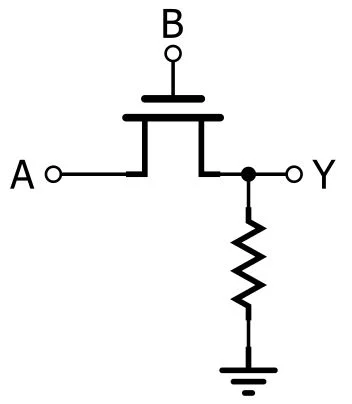

可以使用单个NMOS晶体管作为PTL开关;当施加到栅极的电压为逻辑高时,开关被认为是闭合的,而当施加到栅极的电压为逻辑低时,开关被认为是打开的。下图显示了仅使用一个晶体管的与门(或至少类似于与门的东西)。

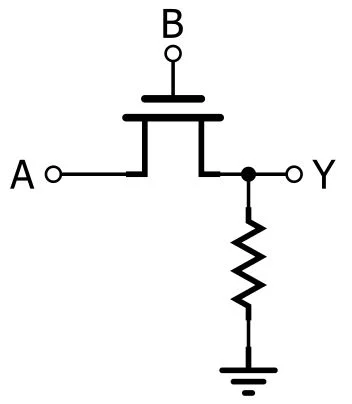

当输入 (A) 为逻辑高且开关控制信号 (B) 为逻辑高时,输出 (Y) 为逻辑高,而对于所有其他组合,输出 (Y) 都不是逻辑高。这听起来像“与”真值表,但我们真的可以将其称为“与”门吗?这取决于你的观点。问题在于,当 B 输入为逻辑低电平时,电路不会驱动逻辑低电平。它只是断开连接,即浮动。为了建立逻辑低电平,我们需要一个下拉电阻:

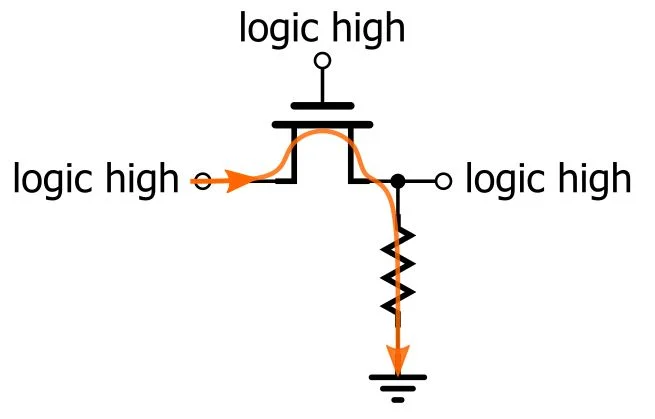

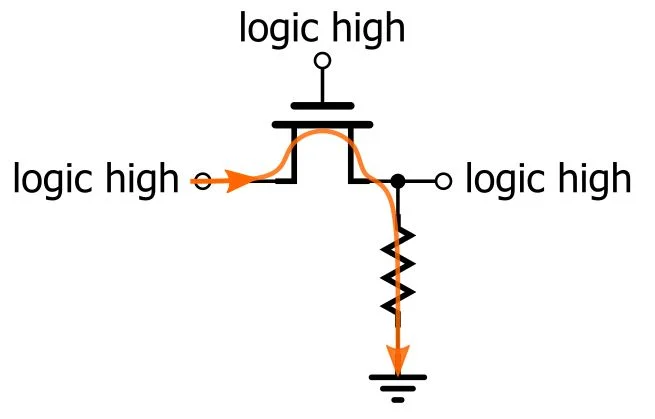

现在我们有了一个功能性与门,并且只使用了一个晶体管和一个电阻器,而基于 CMOS 反相器的标准与门需要六个晶体管。然而,PTL电路绝不等同于标准CMOS版本。首先,它不能可靠地提供低电阻接地路径。其次,只要输出为逻辑高电平,它就会消耗静态功耗——电流从输入流经 NMOS、下拉电阻到地:

这意味着我们失去了基于逆变器的逻辑的一个极其有益的特性,即电源仅在开关期间提供大量电流。 (这就是为什么 CMOS 功耗与频率成正比——更多的开关意味着更多的电流,更多的电流意味着更多的功率。)

传输晶体管逻辑中的 NMOS 与 CMOS

如上一节所示,PTL 围绕 MOSFET 开关构建,这些开关可以传递(因此得名)或阻止信号。使用 NMOS 晶体管作为开关无疑是减少晶体管数量的好方法,但单独的 NMOS 在性能方面并不令人印象深刻。更好的解决方案是 CMOS 传输门:

本文对单独的 NMOS 和 CMOS 传输门进行了简要比较。毫无疑问,一般来说,传输门是更好的实现方式,但请考虑权衡。显然需要一个额外的晶体管,但还要注意,PMOS 不是由开关控制信号驱动,而是由开关控制信号的补码驱动。例如,如果生成输入信号的电路是提供

输出的D 触发器,则这不是问题。不过,通常只有一个输入信号可用,在这种情况下,使用 CMOS 传输门意味着我们还必须有一个反相器来为第二个 FET 创建控制信号。